**New Product**

Preliminary

CBC921 PMRTC

Real-Time Clock/Calendar with Power Manager and Battery Charger

#### Features

- Ultra-low power Real-Time Clock (RTC) with power-fail detect and battery management

- Low power timer and power manager extend run time in battery-powered systems

- Controls 4.1V rechargeable micro-batteries and 3.2V rechargeable coin cells and supercaps; no off-chip components required for battery charger

- Buck charge pump extends backup battery life:

- 15nA RTC using internal RC oscillator

- 50nA RTC using crystal oscillator

- Counters for hundredths, seconds, minutes, hours, date, month, year, century, and weekdays based on a 32.768KHz crystal oscillator or internal RC oscillator

- Automatic leap year calculation

- Alarm capability on all counters

- Two configurable multi-use outputs for interrupts, output clock, and managing sleep mode of external devices

- 64 bytes of RAM

- Internal temperature measurement with 10-bit ADC enables oscillator temperature compensation and temperature read-out

- Advanced crystal calibration to ± 1 ppm

- Ultra-low Iq VIN POR circuit (< 25nA)

- Fixed indicators for PGOOD, charging current on, and charging disabled

- Temperature range -40°C to +85°C

- Serial communication: I<sup>2</sup>C-bus and SPI options

- Lead-free and halogen-free

#### Applications

- **Power bridging** to provide uninterruptible RTC function during exchange of main batteries.

- **Consumer appliances** CBC921 controls switchover from main supply to backup battery.

- Ultra-low power timer draws only 15nA

- Wireless sensors and RFID tags and other powered, low duty cycle applications.

- Business and industrial systems such as: network routers, point-of-sale terminals, single-board computers, test equipment, multi-function printers, industrial controllers, and utility meters.

- Reliable system timekeeping

- Battery-powered devices

- Internet of Things, portable devices

- Daily alarms

3mm x 3mm x 0.55mm 16-pin MLPQ Package

#### **General Description**

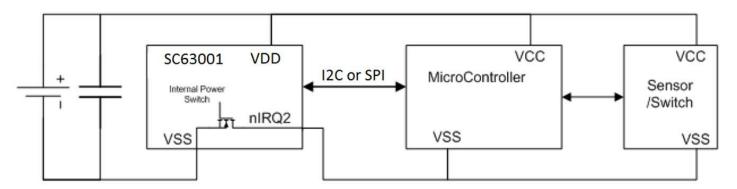

The CBC921xx combines a real-time clock (RTC) with a backup battery charger and other power management features. In the event of an outage of the primary power source, automatic switchover to the backup battery enables extended timekeeping and optionally provides power to external devices to maintain their operation during the power outage.

In normal operation the RTC function is supported by a primary power source, which can be a battery cell, multiple alkaline batteries, or a regulated power supply ranging from 2.85V to 5.5V. The backup battery is charged with a temperaturecompensated voltage derived from the primary voltage source. The backup battery charging is refreshed with a configurable schedule and temperature-dependent duty cycle, both of which are designed to increase service life of the backup battery while minimizing power consumption from the main power source.

The circuit can be used in applications to provide an uninterrupted continuous time clock, calendar function, and time-based interrupts or alarms for wake up from sleep to active mode operation with adjustable intervals to save power in the overall system.

The power management has a low quiescent current and high efficiency for backup battery charging. The RTC circuit has very low quiescent current to extend the RTC run time. The RTC has 2ppm accuracy for clock, calendar, alarm, clock outputs, and interrupt functions. An open drain internal power switch is controlled by interrupts and a sleep manager to facilitate power saving by disconnecting main power from external devices according to user-defined schedules.

© Cymbet 18326 Joplin Street, Elk River, MN 55330 • 763-633-1780 • <u>www.cymbet.com</u> Rev. 4

Preliminary

## Contents

| Pin Configuration (MLPQ-UT16) 2                    |

|----------------------------------------------------|

| Part Numbers                                       |

| Absolute Maximum Ratings                           |

| Thermal Characteristics                            |

| Electrical Characteristics                         |

| Pin Descriptions                                   |

| Block Diagram                                      |

| Functional Description                             |

| Operating Modes and Transitions                    |

| VDD Mode Entry Sequence                            |

| Registers and RTC Management                       |

| Oscillator Selection and Verification              |

| I <sup>2</sup> C Interface                         |

| Limitations to the I <sup>2</sup> C Specifications |

| Slave I <sup>2</sup> C Address Assignment          |

| Supported Formats                                  |

| (1) Direct Format — Write                          |

| (2) Combined Format — Read                         |

| (3) Stop Separated Reads                           |

| Battery Charging                                   |

| Real-Time Clock/Calend                           | dar with Power Manager and Battery Charger | Preliminary |

|--------------------------------------------------|--------------------------------------------|-------------|

| Temperature Measurements and Usage               |                                            |             |

| Application Information                          |                                            |             |

| VOUT Pin Capacitance                             |                                            |             |

|                                                  |                                            |             |

| Register and Memory Map                          |                                            |             |

| Register Settings                                |                                            |             |

| Summary of Interrupts and Timers                 |                                            |             |

| Register Descriptions:                           |                                            | 20          |

| Alarm Registers oxo8-oxoE                        |                                            | 24          |

| Flag Register 0x0F (Read/Clear-Only)             |                                            | 25          |

| Control Registers 0x10-0x11                      |                                            | 25          |

| Interrupt Mask Register 0x12                     |                                            | 27          |

| Clock Output Control Register 0x13               |                                            | 30          |

| Real-Time Clock Calibration Registers: 0x14-0x16 |                                            | 31          |

| Sleep Control Register 0x17                      |                                            |             |

| Timer Management Registers 0x18-0x1A             |                                            |             |

| Charging Control Register 0x1B                   |                                            |             |

| Oscillator and RTC Configuration Registers 0x1C  |                                            | 40          |

| Status Register 0x1D (Read-Only)                 |                                            | 41          |

| Data Transfer Registers 0x22-0x23                |                                            | 42          |

| Battery Management Configuration Registers 0x24  |                                            | 43          |

| Appendix: Charging Duty Cycle Tables             |                                            | 44          |

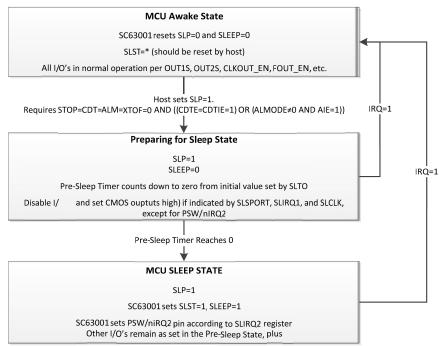

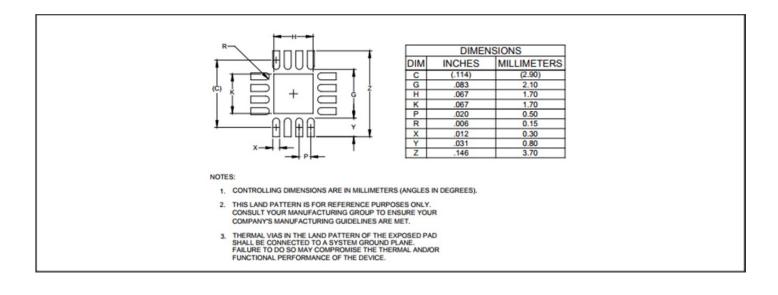

| Outline Drawing - 3x3 MLPQ-UT16                  |                                            | 45          |

| CORPORATION                                           | Real-Time Clock/Calendar with Power Manager and Battery Charger | Preliminary |

|-------------------------------------------------------|-----------------------------------------------------------------|-------------|

| Land Pattern - 3x3 MLPQ-UT16                          |                                                                 | 46          |

| <b>Figures</b><br>Figure 1: Typical application circu | iit for CBC921XXC1                                              | 1           |

| Figure 2: PMRTC block diagram f                       | or bare-die version packaged with a battery                     | 9           |

| Figure 4 Power States and Oper                        | ating Mode Transistions                                         |             |

| Figure 5: VDD Mode Start Up and                       | l Shutdown Sequence                                             |             |

| Figure 6: Bit Transfer on the I2C I                   | 3us                                                             |             |

| Figure 7: I2C Start Stop Protocol.                    |                                                                 |             |

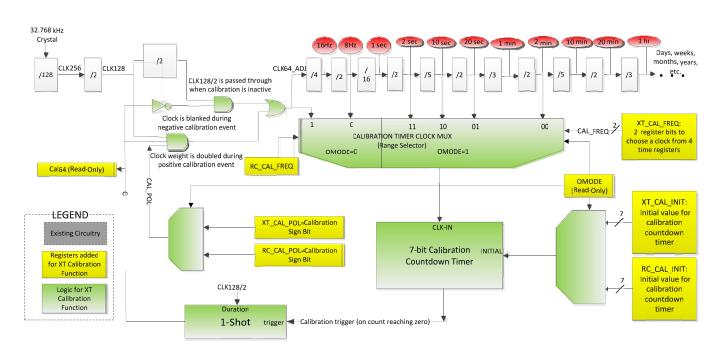

| Figure 9: Block diagram for oscilla                   | ator calibration functionality. Yellow blocks are registers.    |             |

| Figure 10: State diagram represe                      | nting the sleep state controller and associated features        |             |

## Tables

| Table 1: Functions of PWS/nIRQ2 pin determined by OUT2S Register Bits                                        | 27 |

|--------------------------------------------------------------------------------------------------------------|----|

| Table 2:Functions of nPGD/nIRQ pin determined by OUT1S Register Bits                                         | 27 |

| Table 3: Alarm Interrupt signal duration as determined by setting of IM register bits                        | 29 |

| Table 4: Square Wave Output Frequency vs. SQFS Register Setting                                              | 30 |

| Table 5: Calibration timer clock selections as determined by 0x16 B7:B5 and OMODE (0x1D B4)                  | 34 |

| Table 6: Alarm modes determined by ALMODE. X indicates alarm register selected for match detection           | 37 |

| Table 7:Countdown Timer frequency settings for CDTFREQ values                                                | 38 |

| Table 8: Charging Times and Frequencies for full temperature range vs. CHGFREQ and CHGTEMP values            | 39 |

| Table 9: Battery Cutoff Monitoring Frequency Interval (seconds) for settings of BCMFREQ register bits        | 43 |

| Table 10: Charging duty cycles for charge frequency configurations and errors relative to target duty cycles | 44 |

Preliminary

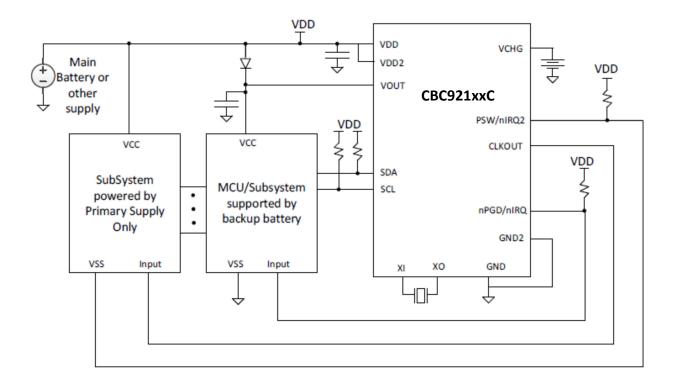

#### **Typical Application Circuit**

Figure 1: Typical application circuit for CBC921xxC

### Part Numbers

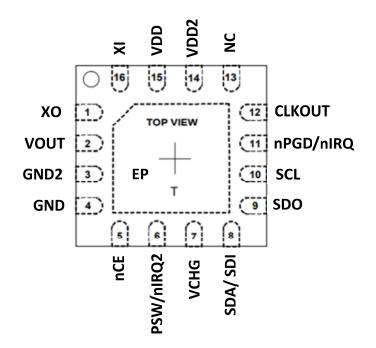

## Pin Configuration (MLPQ-UT16)

| Part      |     |    |                  | Charge  |

|-----------|-----|----|------------------|---------|

| Number    | RTC | PM | I/F              | Voltage |

| CBC92100C | Y   |    | I <sup>2</sup> C |         |

| CBC92100P | Y   |    | SPI              |         |

| CBC92032C |     | Y  | I <sup>2</sup> C | 3.2V    |

| CBC92041C |     | Y  | I <sup>2</sup> C | 4.1V    |

| CBC92032P |     | Y  | SPI              | 3.2V    |

| CBC92041P |     | Y  | SPI              | 4.1V    |

| CBC92132C | Y   | Y  | I <sup>2</sup> C | 3.2V    |

| CBC92141C | Y   | Y  | I <sup>2</sup> C | 4.1V    |

| CBC92132P | Y   | Y  | SPI              | 3.2V    |

| CBC92141P | Y   | Y  | SPI              | 4.1V    |

| CBC92XYYZ Part Numbering   |                               |  |  |  |

|----------------------------|-------------------------------|--|--|--|

| X 1=RTC included, o=no RTC |                               |  |  |  |

| YY                         | Maximum battery charging      |  |  |  |

|                            | voltage (x 10), oo=no battery |  |  |  |

|                            | management included           |  |  |  |

| Z                          | C=I <sup>2</sup> C, P=SPI     |  |  |  |

Preliminary

# Absolute Maximum Ratings

| Parameter                                                 | Symbol                                   | Value             | Units |

|-----------------------------------------------------------|------------------------------------------|-------------------|-------|

| External Supply Input (VDD)                               | V <sub>DD</sub> to V <sub>GND</sub>      | -0.3 to +6.0      | V     |

| Battery Connection Pin (VCHG)                             | V <sub>CHG</sub> to V <sub>GND</sub>     | -0.3 to +4.15     | V     |

| Supply Output Voltage Pin (VOUT)                          | V <sub>OUT</sub> to V <sub>GND</sub>     | -0.3 to +6.0      | V     |

| XI, XO pins in VDD Mode                                   | V <sub>XT_VDD</sub> to V <sub>GND</sub>  | -0.3 to VDD +0.3  | V     |

| XI, XO pins in Backup Mode                                | V <sub>XT_BAT</sub> to V <sub>GND</sub>  | -0.3 to VCHG +0.3 | V     |

| VDD2 pin to VDD pin                                       | V <sub>DD2</sub> to V <sub>DD</sub>      | -0.3 to +0.3      | V     |

| GND2 pin to GND pin                                       | V <sub>GND2</sub> to V <sub>GND</sub>    | -0.3 to +0.3      | V     |

| SCL, SDA/SDI, PSW/nIRQ2, nPGD/IRQ, nCE pins               | V <sub>IO1</sub> to V <sub>GND</sub>     | -0.3 to +6.0      | V     |

| CLKOUT and SDO pins, in Backup and VDD Modes              | V <sub>IO2</sub> to V <sub>GND</sub>     | -0.3 to VDD +0.3  | V     |

| PSW/nIRQ2 pin current                                     | I <sub>PSW</sub>                         | 200               | mA    |

| ESD Protection Level (HBM), VCHG pin <sup>(1)</sup>       | V <sub>CHG_ESD</sub> to V <sub>GND</sub> | TBD               | kV    |

| ESD Protection Level (HBM), all other pins <sup>(1)</sup> | VIO_ESD to VGND                          | 2                 | kV    |

| Operating Temperature                                     | Тј                                       | -40 to +85        | °C    |

| Storage Temperature                                       | T <sub>STG</sub>                         | -65 to +150       | °C    |

Notes:

Exceeding the above specifications may result in permanent damage to the device or device malfunction. Operation outside of the parameters specified in the Electrical Characteristics section is not recommended.

#### Notes:

(1): Tested according to JEDEC standard JESD22-A114-B. No ESD protection is guaranteed on the VCHG pin.

**New Product**

Real-Time Clock/Calendar with Power Manager and Battery Charger

# **Thermal Characteristics**

| Parameter                        | Symbol           | Value | Units |  |

|----------------------------------|------------------|-------|-------|--|

| Thermal Impedance <sup>(2)</sup> | R <sub>eja</sub> | 50    | °C/W  |  |

Notes:

(2): Calculated from package in still air, mounted to 3 x 4.5 (in), 4 layer FR4 PCB per JESD51 standards.

# **Electrical Characteristics**

Unless otherwise specified:  $T_J < 85^{\circ}C$ ,  $-40^{\circ}C < T_A <+85^{\circ}C$ , VDD = 3.6 V, 1uF VDD to GND. Typical values are for  $T_A =+25^{\circ}C$

| Parameter                                                        | Symbol          | Conditions                                                                                        | Min.                | Тур. | Max. | Units |

|------------------------------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------|---------------------|------|------|-------|

| Supply Range                                                     |                 |                                                                                                   |                     |      |      |       |

| VDD Supply Voltage Range                                         | Vdd             |                                                                                                   | VPOR_rising_<br>MAX |      | 5.5  | V     |

| VDD Power-on Reset Rising<br>Threshold                           | VPOR_rising     | Backup to VDD mode entry threshold.                                                               |                     | 2.7  | 2.85 | V     |

| VDD Power-on Reset Falling<br>Threshold                          | VPOR_falling    | Battery backup entry threshold.                                                                   | 2.5                 |      |      | V     |

| VDD Power-on Reset<br>Threshold Hysteresis                       | VPOR_hysteresis | VPOR_rising - VPOR_falling.                                                                       | 90                  | 125  | 170  | mV    |

| VDD POR rising indicator delay, from cutoff mode                 | TdPGD_cutoff    | Measured from VDD crossing VPOR_rising to<br>the falling edge of the nPGD/nIRQ pin,<br>VCHG=2.5V. |                     | 300  |      | ms    |

| VDD POR rising indicator delay,<br>from backup mode              | TdPGD_backup    | Measured from VDD crossing VPOR_rising to<br>the falling edge of the nPGD/nIRQ pin,<br>VCHG=4V.   |                     | 80   |      | ms    |

| Battery Charging Delay<br>Time                                   | TdCHG_rising    | Measured from falling edge of the nPGD/nIRQ pin to rising edge of CHG pin.                        |                     | 40   |      | ms    |

| VOUT Cut-in Time Delay                                           | TdVOUT_rising   | Measured from VDD crossing VPOR_falling<br>threshold to the VOUT switch turn-on.                  |                     | 1    |      | ms    |

| Supply Currents                                                  |                 |                                                                                                   |                     |      |      |       |

| VCHG Supply Current, RC<br>Mode, with Cutoff Monitor<br>Inactive | ICHG_RC4        | Includes RTC operating in RC mode. 4.1V<br>version. VCHG =4.1V. VDD=0 V.                          |                     | 20   |      | nA    |

| VCHG Supply Current, RC<br>Mode, with Cutoff Monitor<br>Inactive | ICHG_RC3        | Includes RTC operating in RC mode. 3.2V version. VCHG =3.2V. VDD=0V.                              |                     | 60   |      | nA    |

**New Product**

### Real-Time Clock/Calendar with Power Manager and Battery Charger

Preliminary

| Parameter                                                        | Symbol               | Conditions                                                                                                                                                                                                     | Min.  | Тур.  | Max. | Units   |

|------------------------------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|------|---------|

| VCHG Supply Current, XT<br>Mode, with Cutoff Monitor<br>Inactive | ICHG_Xtal4           | Includes RTC operating in XTAL mode. 4.1V<br>version. VCHG =4.1V. VDD=0V.                                                                                                                                      |       | 50    |      | nA      |

| VCHG Supply Current, XT<br>Mode, with Cutoff Monitor<br>Inactive | ICHG_Xtal3           | Includes RTC operating in XTAL mode. 3.2V<br>version. VCHG =3.2V. VDD=0V.                                                                                                                                      |       | 150   |      | nA      |

| VCHG Supply Current, XT<br>Mode, with Cutoff Monitor<br>Active   | ICHG_XtalMon         | Includes RTC operating in XTAL mode. 4.1V version only. VCHG =4.1V, VDD=0V.                                                                                                                                    |       | 350   |      | nA      |

| VDD Supply Current with<br>Battery Charging                      | IddCharge            | After POR rising. Excludes battery charging<br>current, but including RTC in Xtal mode. nCE<br>pin held at VDD. SDA/SDI and SCL pins held at<br>VDD or GND. I <sup>2</sup> C bus inactive, other I/O's.<br>not |       | 4000  |      | nA      |

| VDD Supply Current with<br>Battery NOT Charging                  |                      | After POR rising RTC operating in XTAL<br>mode. I2C bus inactive. Other I/O's static.<br>nCE pin held at VDD. SDA/SDI are high or<br>low. No load on CLKOUT/CHGDIS.                                            |       |       |      |         |

| VDD Supply Current in<br>Backup Mode                             | IddPrePor            | VDD=2.5V.                                                                                                                                                                                                      |       | 25    |      | nA      |

| CHG leakage Current, Cutoff<br>Mode                              | I CHG_Cutoff         | VHG=2.5V. VDD=0V. 4.1V version only.                                                                                                                                                                           |       | 70    |      | рА      |

| Battery Charger                                                  |                      |                                                                                                                                                                                                                |       |       |      |         |

| Battery Charger Output<br>Current                                | I CHG_charge         | VCHG=3V.                                                                                                                                                                                                       |       | 50    |      | uA      |

| Battery Charger Output<br>Voltage                                | VCHG4                | 25°C, VDD> VPOR_rising_MAX, 4.1V<br>version.                                                                                                                                                                   | 4.025 | 4.075 | 4.1  | V       |

| Battery Charger Output<br>Voltage                                | VCHG3                | 25°C, VDD > VPOR_rising_MAX, 3.2V<br>version.                                                                                                                                                                  | 3     | 3.1   | 3.2  | V       |

| Battery Charger Output<br>Voltage TC                             | VCHGT <sub>C</sub> 4 | 25°C to 85°C, 4.1V version.                                                                                                                                                                                    |       | -2.2  |      | mV/degC |

| Battery Charger Output<br>Voltage TC                             | VCHGT <sub>C</sub> 3 | 25°C to 85°C, 3.2V version.                                                                                                                                                                                    |       | -1.67 |      | mV/degC |

| Battery Cutoff Threshold                                         | VCHGCutoff           | 4.1V version only.                                                                                                                                                                                             | 2.7   | 3     | 3.3  | V       |

| Oscillator                                                       |                      |                                                                                                                                                                                                                |       |       |      |         |

| RC Oscillator Frequency                                          | FRC                  | Ta=25 °C.                                                                                                                                                                                                      |       | 256   |      | Hz      |

Preliminary

| Parameter                                | Symbol    | Conditions                                        | Min. | Тур.  | Max. | Units |

|------------------------------------------|-----------|---------------------------------------------------|------|-------|------|-------|

| RC Oscillator Frequency<br>Accuracy      | FRC_TOL   | Without calibration; supply between 2.9V and 5.5V | -4   |       | +4   | %     |

| Crystal oscillation frequency            | FXO       |                                                   |      | 32768 |      | Hz    |

| Crystal Internal Load<br>Capacitance     | CLINT     |                                                   |      | 2.5   |      | pF    |

| Crystal Negative Resistance              | RNEG      |                                                   |      | 520   |      | kΩ    |

| Interface Logic                          |           |                                                   |      |       |      |       |

| Logic Input High Threshold               | VIH       | VDD=5.5V                                          | 1.6  |       |      | v     |

| Logic Input Low Threshold                | VIL       | VDD=2.9V                                          |      |       | 0.4  | V     |

| Logic Output High Level                  | VOH       | CMOS outputs                                      |      |       |      | v     |

| Logic Output Low Level                   | VOL       | IL<3mA                                            |      |       | 0.4  | V     |

| Logic Input Leakage                      | ldig_leak |                                                   |      | < 1   |      | nA    |

| Switch On-Resistance                     |           |                                                   |      |       |      |       |

| PSW/nIRQ2/nCHGON Pull<br>Down Resistance | Rpsw      | I_load=100mA                                      |      | 4     |      | Ω     |

| VOUT Switch Resistance                   | RVOUT     | VCHG=4.1V, I_load=1µA                             |      | 1     |      | MΩ    |

| Serial Interface                         |           |                                                   |      |       |      |       |

| I <sup>2</sup> C Clock Frequency         | FI2C      |                                                   |      |       | 400  | kHz   |

**New Product**

Real-Time Clock/Calendar with Power Manager and Battery Charger

Preliminary

# Pin Descriptions

| Pin # | Pin Name  | Pin Type                     | Pin Function (for PM-RTC versions with I <sup>2</sup> C or SPI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------|-----------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | хо        | Analog<br>output<br>(high-Z) | Crystal oscillator connection high-impedance node. Minimize trace length between the crystal and the I.C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2     | VOUT      | Supply Output                | Output voltage providing bias to external circuits in backup mode only. Enabled by VOUTEN register bit. A high-resistance switch and series diode feeding this pin limit the output current and protect the battery.                                                                                                                                                                                                                                                                                                                                                      |

| 3     | GND2      | Ground                       | This pin must be connected to ground (GND).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4     | GND       | Ground                       | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5     | nCE       | Digital Input<br>(CMOS)      | Chip Enable for SPI. Connect this pin to ground when using the I <sup>2</sup> C version.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 6     | PSW/nIRQ2 | Output - Open<br>Drain       | Configurable open-drain output. This pin has a low-resistance switch to ground which can be connected to the ground return of external devices to switch power to those devices. If no interrupt is enabled, PSWEN_WAKE=1, and no other function is configured by the Control Register 2, this pin has the default function of indicating with an active low output if the battery is currently being charged.                                                                                                                                                            |

| 7     | VCHG      | Supply In/Out                | Regulated voltage source output for backup battery charging. Power supply input in backup mode. Connect a battery or other energy storage device between this pin and GND.                                                                                                                                                                                                                                                                                                                                                                                                |

| 8     | SDA/ SDI  | Digital I/O -<br>Open Drain  | Serial data input/output for I <sup>2</sup> C version. Serial data input for SPI version. A pull-up resistor is needed on this bus. A value between 5 K $\Omega$ and 100 K $\Omega$ is recommended depending on the clock frequency of the serial communications.                                                                                                                                                                                                                                                                                                         |

| 9     | SDO       | Digital Output<br>(CMOS)     | Serial data output for SPI version. Leave this pin open when using I <sup>2</sup> C version.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 10    | SCL       | Digital Input<br>(CMOS)      | I <sup>2</sup> C clock/SPI clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 11    | nPGD/nIRQ | Output - Open<br>Drain       | Configurable PGOOD indicator and interrupt1 output. Initially functions as a power good signal, going to an active-low state when the SC63xxx I/O's are ready. At this time, the pin function may be reconfigured by writing to the OUT1S bit through the serial port. Otherwise, this pin will follow the PGOOD register bit, staying active-low until VDD falls below the POR falling threshold. A pull-up resistor to VDD is required to use this pin. Use a maximum value of 200 M $\Omega$ , but a lower value may be needed for higher frequency output selections. |

| 12    | CLK OUT   | Digital Output -<br>CMOS     | Programmable CMOS clock output. Until configured by the clock output control register, this pin has the default function of indicating (with output high) if charging is disabled by either the CHGOFF or CHGRST register bits.                                                                                                                                                                                                                                                                                                                                           |

Preliminary

| Pin # | Pin<br>Name | Pin Type     | Pin Function (for PM-RTC versions with I2C or SPI)                                                                                                                          |

|-------|-------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13    | NC          | Open         | Unused pin, not connected to the I.C.                                                                                                                                       |

| 14    | VDD2        | Supply       | This pin must be connected to the VDD pin.                                                                                                                                  |

| 15    | VDD         | Supply       | Main power source input. Can be connected to the main battery or another voltage source. Place decoupling capacitor of at least 0.1uF between VDD and GND close to the I.C. |

| 16    | XI          | Analog input | Crystal oscillator input; high-impedance node. Minimize trace length between the crystal and the I.C.                                                                       |

| 17    | EP          | Exposed Pad  | Connect the exposed pad to GND.                                                                                                                                             |

Preliminary

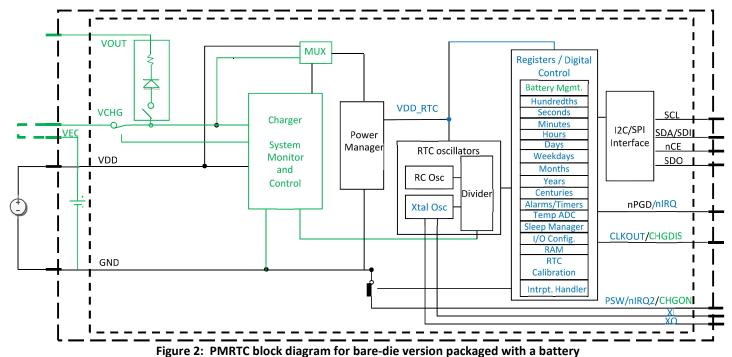

# Block Diagram

Preliminary

# **Functional Description**

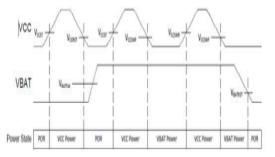

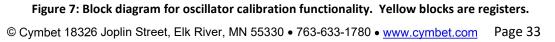

## **Operating Modes and Transitions**

The two operating modes of the CBC92141 are normal operation and backup mode. When the VDD pin is below the POR threshold, the CBC92141 is in backup mode. In backup mode, the CBC92141 operates in an ultra-lower power mode from a power source, typically a battery, connected to the VCHG pin to keep the real time clock running and, if requested and configured accordingly, to supply power to an external load at the VOUT pin. The I/O pins are not available in backup mode, so there are no interrupts or serial communications in this mode The 4.1V version (CBC92141) will shut down to protect the backup battery from over-discharge if the battery voltage falls below the VBatt\_off threshold.

The CBC92141 will be in a non-operational cutoff state initially and whenever the battery voltage falls below the cutoff threshold while VDD is also below the POR threshold. VDD must rise above the POR threshold in order to exit the cutoff state. Figure 9 below illustrates the operating mode transitions and power states.

Figure 3 Power States and Operating Mode Transitions

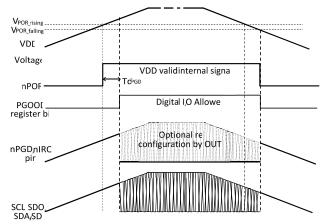

## VDD Mode Entry Sequence

When the external VDD supply rises above the POR threshold, the CBC92141 enters normal operation after a delay  $Td_{PGD}$ , as shown below in Figure **10**. The duration of the Td<sub>PGD</sub> delay depends on whether the CBC92141 is coming out of backup mode or cutoff mode. After the applicable Td<sub>PGD</sub> delay, the nPGD/nIRQ pin will go to an active-low state, indicating that the CBC92141 has disconnected from the backup battery and that the I/O's are ready for communication and signaling. At this time, the external software should use the serial port to rewrite any application-specific values to registers that are not powered in backup mode. In the case of first-time power – up or coming out of cutoff, all application specific register values should be written at this time. After a delay of approximately 40ms the battery charging controller will begin operation. In normal operation the CBC921 will initially and periodically refresh the charge state of the backup battery with a charging voltage and temperature dependent duty cycle based on die temperature. If the OUT1S register bit is not changed the nPGD/nIRQ pin will continue to follow the PGOOD register bit staying active low until VDD falls below the POR falling threshold.

Figure 4: VDD Mode Start Up and Shutdown Sequence

Preliminary

### **Registers and RTC Management**

The RAM and the following registers are powered in backup mode:

- Access Control 0x10

- Charge Control ox1B

- Battery Management ox24

The following are both available and backed up only in the feature PMRTC version:

- Time and Alarm oxoo-oxoE

- Flags oxoF

- Calibration 0x14-16

- Timer Control and Countdown Timer 0x18-19

- OSC and RTC Control ox1C

- RTC data transfer registers 0x22 and 0x23

If the CBC92141 goes into backup mode while the RTC is stopped (e.g., due to resetting the time), it will be automatically restarted so that the system might determine the duration of the power outage and keep general track of time during the outage even if an adjustment was in process.

voltage and duty cycle that depends on the temperature measured in the CBC92141. If the OUT1S register bit is not changed, the nPGD/nIRQ pin will continue to follow the PGOOD register bit, staying active-low until VDD falls below the POR falling threshold.

Countdown, alarm and calibration timers will continue to run in backup mode, except the countdown timer will not repeat once it sets the CDT flag. Registers not listed above, including any associated states such as SLEEP, will be reset to their default values, upon entering normal operation (VDD POR), except that the status register will be updated to reflect any pending interrupts resulting from alarm or countdown timer operations that continued through the backup mode. Also, any flags that were not yet cleared when VDD was lost will generate an interrupt upon return of VDD.

Preliminary

# **Oscillator Selection and Verification**

The CBC92141 generates an internal 256 Hz clock from one of two ultra-low power oscillators depending on the on the Operating state and the value of the OSEL bit in the Oscillator Control register. An OSEL bit value of o selects the internal 256 Hz oscillator, and a value of 1 selects the 32.786 kHz crystal (XT) oscillator. Upon initial power-up, the RC oscillator is used for timekeeping and internal logic The OSEL bit can be toggled by the serial communications port to switch between the RC and XT oscillators. The system might do this to reduce power consumption, which is lower using the RC oscillator, or if the system controller detects an XT frequency error well beyond the calibration capabilities of the system. Using the AOS register bit, the CBC92141 can be configured to automatically switch to the RC oscillator upon entering backup mode.

Switching between the XT and RC Oscillators is guaranteed to produce less than 10 milliseconds of error in the Calendar Counters., but this error could accumulate over time if there is frequent switching between the oscillators, as might be done to periodically check the functionality of the XT oscillator.

# I<sup>2</sup>C Interface

The CBC92141C has a slave I<sup>2</sup>C interface that supports standard and fast mode data rates and combined format operations and is compliant with the I<sup>2</sup>C standard version 6.0 April 2014.

# Limitations to the I<sup>2</sup>C Specifications

The CBC92141 only recognizes seven bit addressing. This means that ten bit addressing and CBUS communication are not compatible. The device can operate in either standard mode (100kbit/s) or fast mode (400kbit/s).

# Slave I<sup>2</sup>C Address Assignment

The CBC92141 has the slave address byte 1010101x for I<sup>2</sup>C communications. The eight bit is the direction bit.

### Supported Formats

The supported formats are described in the following subsections and illustrated in the following subsections.

© Cymbet 18326 Joplin Street, Elk River, MN 55330 • 763-633-1780 • <u>www.cymbet.com</u> Page 12

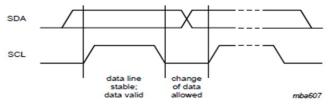

I<sup>2</sup>C is a two-wire serial interface where the two lines are serial clock (SCL) and serial data (SDA). SDA must be connected to a positive supply through an external pull-up resistor. The devices communicating on this bus can drive the SDA line low or release it to high impedance. An external device that initiates the I<sup>2</sup>C transaction becomes the master of the bus. Communication is initiated by the master sending a Start condition, a high-to-low transition on SDA, while the SCL line is high. After the Start condition, the device address byte is sent, most significant bit (MSB) first, including the data communications. The eighth bit is the data direction bit.

Figure 5: Bit Transfer on the I2C Bus

Preliminary

## (1) Direct Format — Write

The simplest format for an I<sup>2</sup>C write is direct format. After the start condition [S], the slave address is sent, followed by an eighth bit indicating a write. The CBC92141C then acknowledges that it is being addressed, and the master responds with an 8 bit data byte consisting of the register address. The slave acknowledges and the master sends the a 8-bit data byte to be written. Once again, the slave acknowledges and the master either terminates the transfer with the stop condition [P], as shown in , or sends additional 8 bit data bytes (each to be acknowledged by the slave) before terminating. Upon writing data to a register, the CBC92141C automatically increments the register address pointer for subsequent data received in the write operation.

### (2) Combined Format — Read

After the start condition [S], the slave address is sent, followed by an eighth bit indicating a write. The CBC92141C then acknowledges that it is being addressed, and the master responds with an 8-bit data byte consisting of the target register address. The slave acknowledges and the master sends the repeated start condition [SR]. Once again, the slave address is sent, followed by an eighth bit indicating a read. The slave responds with an acknowledge and the 8 bit data from the target register. If the master then sends an ACK, the slave will auto-increment the register address and send the 8bit data from the new address. The ACK and auto-increment read may continue until the master terminates the read operation by sending a non-acknowledge (NACK) and terminating the transfer with the stop condition [P]. Figure 14 shows the Combined Format Read operation for the case in which a single byte is read.

## (3) Stop-Separated Reads

Stop-separated reads can also be used. This format allows a master to set up the register address pointer for a read and return to that slave at a later time to read the data. In this format the slave address followed by a write command are sent © Cymbet 18326 Joplin Street, Elk River, MN 55330 • 763-633-1780 • <u>www.cymbet.com</u> Page 13

after a start [S] condition. The CBC92141C then acknowledges it is being addressed, and the master responds with the 8-bit register address. The master sends a stop or restart condition and may then address another slave. After performing other tasks, the master can send a start or restart condition to the CBC92141C with a read command. The device acknowledges this request and returns the data from the register location that had previously been set up as the target.

As with the Combined Format – Read operation, the master can send a NACK and terminate the operation with a stop [P] condition, or it can send an ACK to read more data in one or more serially auto-incremented register locations.

<sup>1</sup> From UM10204, I<sup>2</sup>C-bus specification and user manual, Rev. 6 — 4 April 2014, NXP Semiconductor

Preliminary

### **Hundredths Count Generation**

The SC63141 generates a very approximate 100 Hz clock from the high-accuracy internal 256 Hz clock and uses this 100 Hz clock to update the hundredths- and tenths-of-asecond time register counts and to offer a 100 Hz clock option for square wave outputs and other timing features. Each cycle of the 100 Hz clock consists of 2 to 4 cycles of the 256 Hz clock. There are 4 cycles of 256 Hz in the first hundredths count period after the clock is reset (once per second). The other 99 hundredths counts consist of 2 or 3 256Hz clock cycles, alternating between 7 counts of 2 x 256Hz clock cycles and 9 counts of 3 x 256Hz clock cycles, with the exception of first set of 2 cycle counts, which includes the extra 2 cycles in the first 100th count. Except for the first cycle of each second, the resulting edge-to- edge clock jitter error is +22/-25%.

**CBC921 PMRTC**

#### Real-Time Clock/Calendar with Power Manager and Battery Charger

Preliminary

## **Battery Charging**

During normal operation, the CBC92141 charges the backup battery (or other energy storage device) connected to the VCHG pin, with a temperature dependent duty-cycle, frequency and charging voltage.

Upon entering normal operation (VDD rising above POR level), the CBC92141 will initially charge the backup battery for at least 72 hours and no more than 96 hours. After this initial charging duration, the SC630001 will periodically run a refresh charging operation to replenish charge lost by battery selfdischarge and the leakage current from the circuit connected to the battery. These discharge effects on the battery should be very small but can accumulate over time, especially at higher temperatures, and circuit leakage currents would have a larger impact on a smaller, lower capacity battery. Accordingly, the CBC92141 has registers for the user to configure the charging frequency and to additionally configure an incrementally higher charging frequency at temperatures of +40°C or higher. This configurability enables the user to optimize the trade-offs among power draw from the primary source (at VDD), backup battery run-time, and longer backup battery life, as battery life is typically improved by leaving the battery at a lower state of charge. Also, for applications subject to large temperature changes over the course of a few days or weeks, users may prefer to configure more frequent charging cycles to correct for the effects of temperature on battery voltage. In particular, for the case that the battery is charged at a moderate or low temperature and then the temperature rises above +40C, the next charge cycle will apply the temperature compensated charging voltage and reduce the battery voltage to avoid degradation of the battery. Once a charging cycle begins, the charging frequency and charging on-time are locked in regardless of changes to the Battery Management register. However, the CHGNOW bit can be set to force a VDD POR event, which effectively reboots the charging process, including initial charging, followed by synchronization to the schedule called for in the Battery Management register.

Table 8 in the Battery Management register description section provides the charging frequencies and charger on- times corresponding to the relevant temperature ranges and the user configuration settings of the CHGFREQ and CHGTEMP register bits. temperatures between 25°C and 85°C, a temperature coefficient of Vbattemp\_coeff is applied to reduce the charging voltage in 4°C steps to maintain good battery life. If the die temperature increases such that the temperature compensated charging voltage is less than the battery voltage, then the battery charging circuit will (during its scheduled charging ontime period) sink a small amount of current to gradually discharge the battery to the target voltage.

### Temperature Measurements and Usage

The CBC92141 includes an internal temperature measurement circuit and a 10-bit ADC to store temperature readings in the TEMPADC registers. Temperature measurements can be used by an external MCU to adjust RTC calibration parameters. The CBC92141 measures the temperature at the beginning of each charge cycle and uses this measurement to set the battery charging voltage, charger on-time, and the charging frequency time interval. This interval defines the delay until the next time that the temperature will be measured and a new charge cycle will begin. As detailed in Table 8, the charging frequency interval can vary from 4 hours to 32 days. The MEAS\_TEMP bit in a separate register can be used for external requests to update the temperature measurement. Updating the temperature measurement will update values stored in the TEMPADC registers and will immediately update the temperaturecompensation of the charging voltage. However, mid-cycle temperature updates will not affect the charging frequency and charging period, which will only be updated from the temperature measurement at the beginning of the next charge cycle.

The CBC92141 uses its internal temperature measurements to adjust the voltage applied to the battery. For temperatures of 25°C or less, the charging voltage is set to VBatt. For © Cymbet 18326 Joplin Street, Elk River, MN 55330 • 763-633-1780 • <u>www.cymbet.com</u> Page 15

Preliminary

### **Application Information**

#### **VOUT Pin Capacitance**

The user typically needs to place some holdup capacitance on the VOUT pin to bridge the transition into and out of backup mode. The amount of capacitance needed will depend on the application requirements according to the following equation:

CVOUT\_min = ILOAD\_max \* TdVOUT\_rising (max) / (VPOR\_falling (min) - VVOUT\_min)

Where

ILOAD\_max is the maximum external loading current on the VOUT bus;

VVOUT\_min is the minimum voltage that the application can accept at the VOUT pin during the switch-over transient;

CVOUT\_min is the minimum capacitance needed on the VOUT bus;

TdVOUT\_rising (max) is the maximum VOUT Cut-in Time delay spec. (See TdVOUT\_rising in Electrical Characteristics table.)

VVOUT\_min is the maximum external loading of the VOUT pin;

VPOR\_falling (min) is the minimum falling VDD voltage that will trigger the CBC92141 POR function. (See VPOR\_falling in Electrical Characteristics table.)

Note that a nominal capacitance of at least twice the minimum value is typically needed with X7\* or X5\* ceramic capacitors to account for capacitance variation with DC bias voltage, initial tolerance, and temperature tolerance. Check the manufacturers specifications to account for these effects.

In the case of an external power source at VOUT that provides partial support of the loading during the switch-over transient, , the minimum capacitance requirement would be reduced based on available charge from the external power source. For example, there might be a battery that is nearly drained but still has some capacity.

Preliminary

## **Register and Memory Map**

Registers are accessed by selecting a register address and then performing read or write operations. The table below lists the contents of each register. Descriptions of register variables follow later in the document. Registers are read/write type unless noted as read-only. "X"'s indicates unused registers, which return a value of zero when read.

| Color code: RTC-only bits, PM-only bits. Contents of green highlighted registers are reset to default values on VDD mode entry. |                |                            |          |                 |           |                    |           |           |              |        |

|---------------------------------------------------------------------------------------------------------------------------------|----------------|----------------------------|----------|-----------------|-----------|--------------------|-----------|-----------|--------------|--------|

| Offset                                                                                                                          | Reset<br>Value | Register                   | B7       | B6              | В5        | B4                 | B3        | B2        | B1           | В0     |

|                                                                                                                                 |                |                            | Time and | Date Registers  | 5         |                    |           |           |              |        |

| 0x00                                                                                                                            | 0x00           | Hundredths/Tenths          |          | Seconds - Tent  | hs        |                    |           | Seconds - | Hundred      | ths    |

| 0x01                                                                                                                            | 0x00           | Seconds                    | Х        | Seco            | ond- Tei  | าร                 |           | Seco      | nd-ones      |        |

| 0x02                                                                                                                            | 0x00           | Minutes                    | х        | Minu            | ites- Te  | ns                 |           | Minut     | es-ones      |        |

| 0x03                                                                                                                            | 0x00           | Hours (24 Hr Mode)         | Х        | x               | Но        | urs-Tens           | н         | ours-ones |              |        |

| 0x03                                                                                                                            | 0x00           | Hours (12 Hr Mode)         | Х        | x               | AM/<br>PM | Hour-<br>Tens      | н         | ours-ones |              |        |

| 0x04                                                                                                                            | 0x00           | Date                       | х        | x               | Da        | te-Tens            | Date-Ones |           |              |        |

| 0x05                                                                                                                            | 0x00           | Months                     | х        | x               | x         | Months-<br>tens    |           | Mont      | hs-ones      |        |

| 0x06                                                                                                                            | 0x00           | Years                      |          | Year - Tens     |           |                    | Y         | ear-ones  |              |        |

| 0x07                                                                                                                            | 0x00           | Weekdays                   | х        | х               | х         | x x                |           |           | Day of W     | eek    |

|                                                                                                                                 |                |                            | Alarn    | n Registers     |           |                    |           |           |              |        |

| 0x08                                                                                                                            | 0x00           | Hundredths/Tenths<br>Alarm | Seco     | onds- Alarm - 1 | renths    |                    | Sec       | onds Alar | m- Hund      | redths |

| 0x09                                                                                                                            | 0x00           | Seconds Alarm              | х        | Second          | s ALM     | Tens               |           | Seconds   | ALM-one      | es     |

| 0x0A                                                                                                                            | 0x00           | Minutes Alarm              | х        | Minute          | s ALM-    | Tens               |           | Minutes   | ALM-one      | es     |

| 0x0B                                                                                                                            | 0x00           | Hours Alarm (24 Hr Mode)   | Х        | х               |           | rs Alarm -<br>Tens |           | Hours /   | ALM-one:     | 5      |

| 0x0B                                                                                                                            | 0x00           | Hours Alarm (12 Hr Mode)   | Х        | x               | AM/P<br>M | Hrs ALM -<br>Tens  |           | Hours /   | irs ALM-ones |        |

| 0x0C                                                                                                                            | 0x00           | Date Alarm                 | X X Da   |                 |           | ALM-Tens           |           | Date A    | LM-Ones      |        |

© Cymbet 18326 Joplin Street, Elk River, MN 55330 • 763-633-1780 • <u>www.cymbet.com</u> Page 17

Preliminary

| 0x0D | 0x00 | Months Alarm        | Months Alarm X |       | x | Months<br>ALM-<br>Tens | Months ALM-ones |                   |  |

|------|------|---------------------|----------------|-------|---|------------------------|-----------------|-------------------|--|

| 0x0E | 0x00 | Weekdays ALM        | х              | х     | x | х                      | х               | Day of Week Alarm |  |

| 0x1C | 0x00 | RTC and OSC Control | OSEL           | 12/24 | x | CENT                   | AOS             | х                 |  |

| 0x1D | 0x00 | Stas Read Only      | PSWON          | 12/24 | x | CENT                   | AOS             | Х                 |  |

Preliminary

| Off-<br>set | Reset<br>Value                      | Register                               | 7               | 6                   | 5             | 4              | 3                             | 2         | 1              | 0    |

|-------------|-------------------------------------|----------------------------------------|-----------------|---------------------|---------------|----------------|-------------------------------|-----------|----------------|------|

| Γ           |                                     | r coding of<br>(reset) values          | pre-NVM<br>load | RTC-only<br>version |               | -only<br>rsion | full-feature<br>all if not ot |           |                |      |

|             | PM ena                              | abled trim bit                         | 0               | 0                   |               | 1              |                               |           |                |      |

|             | RTC en                              | abled trim bit                         | 0               | 1                   |               | 0              |                               | 1         |                |      |

|             |                                     | r-code for<br>ter defaults             | red             | blue                | gr            | een            |                               | black     |                |      |

| 0x0F        | 0x00                                | <u>Flags</u><br>(Read/Clear-Only)      | SLST            | XTOF                | х             | х              | CDT                           | ALM       | x              | х    |

| 0x10        | 0x00                                | Access Control                         | STOP            | x                   | x             | x              | x                             | x         | WBATM<br>AN    | WRTC |

| 0x11        | 0x00                                | Output Control                         | x               | OUTA                | OUTB          |                | OUT2S                         |           | ou             | T1S  |

| 0x12        | 0x00<br>0xEC<br><b>0x02</b><br>0xEC | Interrupt Mask                         | OFIE            | IN                  | IM X          |                | CDTIE                         | AIE       | ENPSW_<br>WAKE | x    |

| 0x13        | 0x0B<br>(all<br>cases)              | Clock Output<br>Control                | SQWE            | CLKOUT_<br>EN       | FOUT_<br>EN   | x              |                               | SC        | QFS            |      |

| 0x14        | 0x00                                | XT Calibration<br>Configuration        | XTCAL_<br>POL   |                     |               |                | XTCAL_INI                     | Г         |                |      |

| 0x15        | 0x00                                | <u>RC Calibration</u><br>Configuration | RCCAL_<br>POL   |                     |               | RCCAL_INIT     |                               |           |                |      |

| 0x16        | 0x00                                | <u>Oscillat</u><br>Calibration Range   |                 | L_CLK               | RCCAL<br>_CLK |                | х                             |           |                |      |

| 0x17        | 0x00                                | Sleep Control                          | SLP             | SLIRQ1              | SLIRQ2        | SLPORT         | SLCLK                         |           | SLTO           |      |

| 0x18        | 0x00                                | Timer Control                          | CDTE            | CDRPT               |               | A              | LMODE                         |           | CDTFREQ        |      |

| 0x19        | 0x00                                | <u>Countdown Time</u><br>(Read-only)   | -               |                     | CDTII         | ME = Coun      | tdown Timer                   | Value     |                |      |

| 0x1A        | 0x00                                | Countdown Initial                      |                 |                     | CDTINIT       | = Countdo      | own Timer Init                | ial Value |                |      |

| 0x1B        | 0x80<br>0x80<br>0x09<br>0x09        | Charge Control                         | CHGOFF          | CHGNOW              | CHGRST        | x              | CHGFREQ                       |           | CHGTI          | EMP  |

© Cymbet 18326 Joplin Street, Elk River, MN 55330 • 763-633-1780 • <u>www.cymbet.com</u> Page 19

### **Register Settings**

### **Summary of Interrupts and Timers**

Note: Flags must be cleared for respective interrupt to be re-generated on repeat timer events.

| Interrupt | Function              | Interrupt | Duration                         | Timer   | Flag |

|-----------|-----------------------|-----------|----------------------------------|---------|------|

|           |                       | Enabler   |                                  | Enabler |      |

| AIRQ      | Alarm Match           | AIE       | Determined by IM (0x12 B6:B5)    | ALMODE  | ALM  |

| TIRQ      | Countdown Timer       | CDTIE     | Determined by IM (0x12 B6:B5)    | CDTE    | CDT  |

| OFIRQ     | Oscillator Failure    | OFIE      | Level held until flag is cleared | N/A     | XTOF |

| IRQ       | AIRQ or TIRQ or OFIRQ |           |                                  |         |      |

### **Register Descriptions:**

### **Clock/Calendar Registers**

Note: WRTC must be set to 1 to allow writing to clock/calendar registers 0x01-0x07

| Offset | Bits  | Register         | Description                                                                       |

|--------|-------|------------------|-----------------------------------------------------------------------------------|

| 0x00   | B7:B4 | Seconds - Tenths | The tens digits of the hundredths of seconds approximation. See hundredths below. |

Preliminary

| 0x00  | B3:B0      | Seconds -<br>Hundredths |                                     |    |    | -   |    |    |     |    |  |  |

|-------|------------|-------------------------|-------------------------------------|----|----|-----|----|----|-----|----|--|--|

| 0x001 | B7         | Not Used                | Minutes/Seconds Registers BCD Table |    |    |     |    |    |     |    |  |  |

|       |            |                         | Decimal                             |    | Те | ens |    | Or | nes |    |  |  |

|       |            |                         | Time                                | B6 | B5 | B4  | B3 | B2 | B1  | B0 |  |  |

| 0x01  | B6:B4      | Seconds - Tens          | Count                               | 40 | 20 | 10  | 8  | 4  | 2   | 1  |  |  |

|       |            |                         | 0                                   | 0  | 0  | 0   | 0  | 0  | 0   | 0  |  |  |

|       |            |                         | 1                                   | 0  | 0  | 0   | 0  | 0  | 0   | 1  |  |  |

|       |            | Seconds - Ones          | 2                                   | 0  | 0  | 0   | 0  | 0  | 1   | 0  |  |  |

| 0x01  | B3:B0      |                         |                                     |    |    |     |    |    |     |    |  |  |

|       |            |                         | 9                                   | 0  | 0  | 0   | 1  | 0  | 0   | 1  |  |  |

| 0x02  | B7         | Not Used                | 10                                  | 0  | 0  | 1   | 0  | 0  | 0   | 0  |  |  |

| 0702  |            | Not osed                | . 11                                | 0  | 0  | 1   | 0  | 0  | 0   | 1  |  |  |

|       |            |                         | 12                                  | 0  | 0  | 1   | 0  | 0  | 1   | 0  |  |  |

| 0x02  | B6:B4      | Minutes - Tens          | 13                                  | 0  | 0  | 1   | 0  | 0  | 1   | 1  |  |  |

|       |            |                         |                                     |    |    |     |    |    |     |    |  |  |

|       |            |                         | 57                                  | 1  | 0  | 1   | 0  | 1  | 1   | 1  |  |  |

|       |            |                         | 58                                  | 1  | 0  | 1   | 1  | 0  | 0   | 0  |  |  |

| 0x02  | 0x02 B3:B0 | Minutes - Ones          | 59                                  | 1  | 0  | 1   | 1  | 0  | 0   | 1  |  |  |

|       |            |                         |                                     |    |    |     |    |    |     |    |  |  |

|       |            |                         |                                     |    |    |     |    |    |     |    |  |  |

| 0x03 | B7:B6                    | Not Used                    |             | 2  | 4-Ho        | ur Mo | ode   |      |    | [ |             |     | 12-hour        | mode |            |        |    |

|------|--------------------------|-----------------------------|-------------|----|-------------|-------|-------|------|----|---|-------------|-----|----------------|------|------------|--------|----|

|      |                          | Hours-                      |             |    | urs-<br>ens | F     | lours | -One | s  |   | 12-<br>hour | AM/ | Hours<br>-Tens |      | Hours-Ones |        |    |

| 0x03 | 0x03 B5:B4               | Tens<br>(24-hour<br>mode)   | 24-<br>hour | B5 | B4          | B3    | B2    | B1   | B0 |   | count       | PM  | B4             | B3   | B2         | B1     | В0 |

|      |                          | modej                       | count       | 20 | 10          | 8     | 4     | 2    | 1  |   |             |     | 10             | 8    | 4          | 2      | 1  |

|      |                          |                             | 0           | 0  | 0           | 0     | 0     | 0    | 0  |   | 12          | 0   | 1              | 0    | 0          | 1      | 0  |

|      |                          | AM/PM                       | 1           | 0  | 0           | 0     | 0     | 0    | 1  |   | 1           | 0   | 0              | 0    | 0          | 0      | 1  |

| 0x03 | 003 B5 (12-hour<br>mode) | 2                           | 0           | 0  | 0           | 0     | 1     | 0    |    | 2 | 0           | 0   | 0              | 0    | 1          | 0      |    |

|      |                          | moue)                       |             |    |             |       |       |      |    |   |             |     |                |      |            |        |    |

|      |                          |                             | 9           | 0  | 0           | 1     | 0     | 0    | 1  |   | 9           | 0   | 0              | 1    | 0          | 0      | 1  |

|      |                          | Hours-                      | 10          | 0  | 1           | 0     | 0     | 0    | 0  |   | 10          | 0   | 1              | 0    | 0          | 0      | 0  |

| 0x03 | B6                       | Tens                        | 11          | 0  | 1           | 0     | 0     | 0    | 1  |   | 11          | 0   | 1              | 0    | 0          | 0      | 1  |

| UXUS | БО                       | (12-hour                    | 12          | 0  | 1           | 0     | 0     | 1    | 0  |   | 12          | 0   | 1              | 0    | 0          | 1      | 0  |

|      |                          | mode)                       | 13          | 0  | 1           | 0     | 0     | 1    | 1  |   | 1           | 0   | 0              | 0    | 0          | 0      | 1  |

|      |                          |                             |             |    |             |       |       |      |    |   | 7           | 0   | 0              | 0    | 1          | 1      | 1  |

|      |                          | Hours-                      | 19          | 0  | 1           | 1     | 0     | 0    | 1  |   | 8           | 0   | 0              | 0    | 1          | 1<br>0 | 1  |

|      |                          | ones                        | 20          | 1  | 0           | 0     | 0     | 0    | 0  |   | <u> </u>    | 0   | 0              | 1    | -          |        | 0  |

| 0x03 | 0x03 B3:B0               | (12-hour<br>and 24-<br>hour | 21          | 1  | 0           | 0     | 0     | 0    | 1  |   | -           | -   | 0              | 1    | 0          | 0      | 1  |

|      |                          |                             | 22          | 1  | 0           | 0     | 0     | 1    | 0  |   | 10          | 0   | 1              | 0    | 0          | 0      | 0  |

|      |                          | modes)                      | 23          | 1  | 0           | 0     | 0     | 1    | 1  |   | 11          | 0   | 1              | 0    | 0          | 0      | 1  |

© Cymbet 18326 Joplin Street, Elk River, MN 55330 • 763-633-1780 • www.cymbet.com Page 21

Preliminary

| 0x04  | B7:B6      | Not Used       |          |                      | Day    | /s Re | egist | ter BC | D Ta  | ble    |     |    |

|-------|------------|----------------|----------|----------------------|--------|-------|-------|--------|-------|--------|-----|----|

| 0x04  | в7:во      | Not Osed       |          |                      | т      | ens   |       |        | C     | Dnes   |     |    |

|       |            |                |          | Date                 | B5     | В     | 4     | B3     | B2    | В      | 1 6 | B0 |

|       |            |                |          | 1                    | 0      | (     | )     | 0      | 0     | (      | )   | 1  |

| 0x04  | B5:B4      | Date           |          | 2                    | 0      | (     | )     | 0      | 0     |        | 1   | 0  |

| 0.00- | 53.54      | (Tens)         |          |                      |        |       |       |        |       |        |     |    |

|       |            |                |          | 9                    | 0      | (     | )     | 1      | 0     | (      | )   | 1  |

|       |            |                |          | 10                   | 0      | 1     | 1     | 0      | 0     | (      | )   | 0  |

|       |            |                |          | 11                   | 0      | 1     | 1     | 0      | 0     | (      | )   | 1  |

|       |            |                |          | 12                   | 0      | 1     | 1     | 0      | 0     |        | 1   | 0  |

|       |            |                |          | 13                   | 0      | 1     | 1     | 0      | 0     |        | 1   | 1  |

|       |            |                |          |                      |        |       |       |        |       |        |     |    |

|       |            |                |          | 26                   | 1      | _     | )     | 0      | 1     | -      |     | 0  |

|       |            | Data           |          | 27                   | 1      | -     | )     | 0      | 1     | -      |     | 1  |

| 0x04  | B3:B0      | Date<br>(Ones) |          | 28                   | 1      | _     | )     | 1      | 0     |        |     | 0  |

|       |            | (Ones)         |          | 29                   | 1      |       | )     | 1      | 0     | -      |     | 1  |

|       |            |                |          | 30                   | 1      | -     | 1     | 0      | 0     |        |     | 0  |

|       |            |                |          | 31                   | 1      | 1     | 1     | 0      | 0     | (      | )   | 1  |

| 0x05  | B7:B5      | Not Used       | г        |                      |        |       |       |        |       |        |     |    |

|       |            |                |          |                      | Mon    |       |       | ster E | SCD I |        |     |    |

|       |            |                |          |                      |        | Tens  |       |        |       |        | nes | 1  |

|       |            |                |          | Month                |        | B5    | B4    | -      |       | B2     | B1  | B0 |

|       |            |                | -        |                      |        | 20    | 10    | 2      | 8     | 4      | 2   | 1  |

| 0.05  | <b>D</b> 4 | Months-        | -        | January              | c      | )     | 0     | 0      |       | 0      | 0   | 1  |

| 0x05  | B4         | tens           | -        | February             | C      |       | 0     | 0      |       | 0      | 1   | 0  |

|       |            |                |          | March                | c      |       | 0     | 0      |       | 0      | 1   | 1  |

|       |            |                |          | April                | C      |       | 0     | 0      |       | 1      | 0   | 0  |