# **Analog Front End with High Gain PGA**

#### **■ FEATURES**

Supply Voltage +2.7V to +3.6VAmbient Operating Temperature

-40°C to +125°C

ADC Resolution 16-Bit (No missing codes)

Data Rate 0.814k to 6.51ksps<sup>(1)</sup>

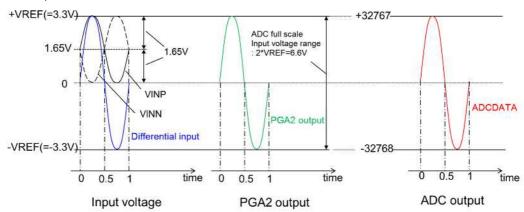

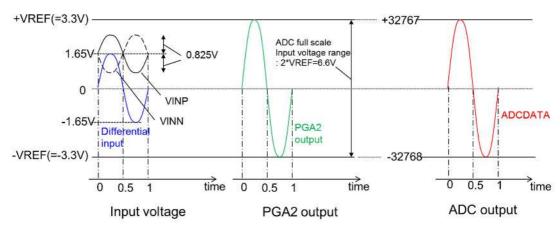

•Input mode Differential

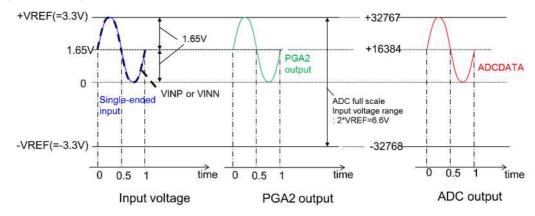

Single-ended (2)

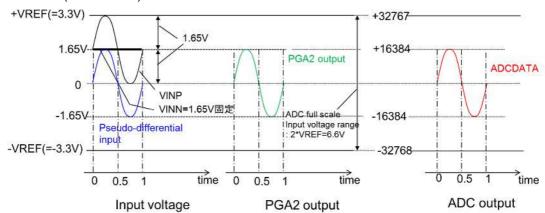

Pseudo-differential (3)

PGA 1V/V to 512V/V

System Calibration for offset & gain drift

Conversion mode Single / Continuous

●Interface SPI

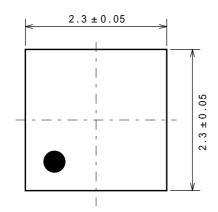

•Package DFN8 (ESON8-V1) / 2.3mm x 2.3mm

SSOP8 / 3.5mm x 6.4mm

(1) Case of single conversion.

(Continuous conversion is three times the data rate.)

(2) PGA2 can be used only. (PGA1 cannot be used.) Two channels of VINP & VINN can be used.

(3) Bias voltage of VINP & VINN is common to VDD / 2. Input Signal can be used VINP only.

#### ■ APPLICATION

- Pressure sensors

- Flowmeters

- Thermostat

- PLC

- Digital Panel Meters

#### **■** GENERAL DESCRIPTION

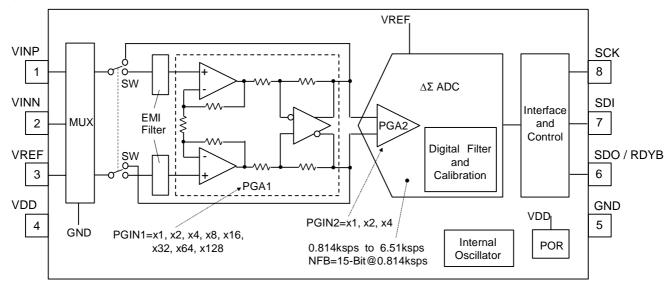

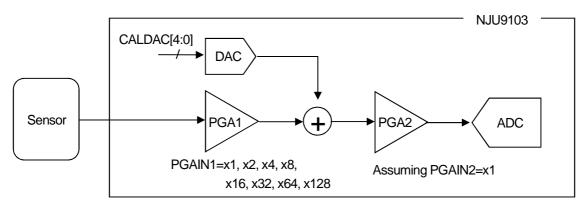

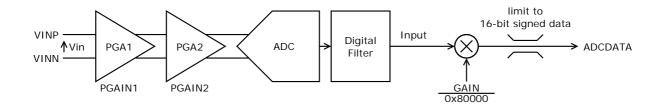

NJU9103 is a small size AFE with up to 512 times internal PGA (Programmable Gain Amplifier). Internal 16-bit  $\Delta\Sigma$  type A / D converter can perform conversion rates from 0.814ksps to 6.51ksps.

The customer can choose internal A/D converter's input, among single-ended input, differential input and pseudo-differential input.

NJU9103 can set the optimum gain to the pressure sensor, flow sensor by a wide range of gain setting. Sensor of the offset is corrected by internal D / A converter. Various parameters (such as gain, conversion rate, correction) settings can be easily set in the SPI communication from an external MCU.

NJU9103 will contribute to the customer's development time reduction and the series product release. NJU9103 is also can be mounted in a narrow application footprint by a small 8-pin package. Package is preparing the DFN and SSOP

## **■ EQUIVALENT CIRCUIT BLOCK DAIGRAM**

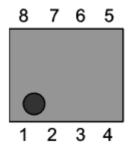

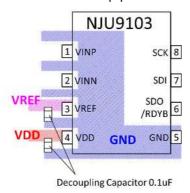

## **■ PIN CONFIGURATION**

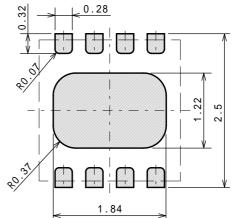

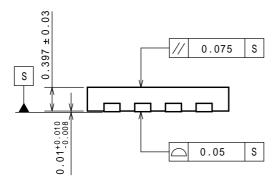

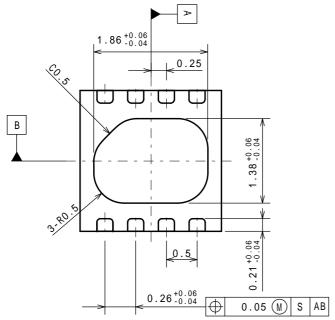

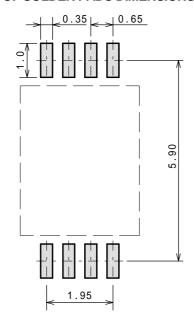

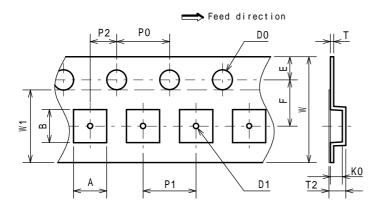

## DFN8 (ESON8-V1)

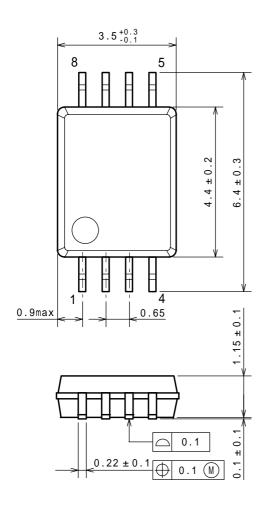

## SSOP8

| PIN NO. | SYMBOL                                | PIN TYPE                                                    |

|---------|---------------------------------------|-------------------------------------------------------------|

| 1       | VINP                                  | +INPUT for differential mode / INPUT1 for Single-ended mode |

| 2       | VINN                                  | -INPUT for differential mode / INPUT2 for single-ended mode |

| 3       | VREF                                  | Reference Voltage Input                                     |

| 4       | VDD                                   | Supply Voltage                                              |

| 5       | GND                                   | GND                                                         |

| 6       | SDO/RDYB                              | SPI serial data output / RDYB output                        |

| 7       | SDI                                   | SPI serial data input                                       |

| 8       | SCK                                   | SPI serial clock input                                      |

| *(1)    | Exposed PAD<br>DFN8(ESON8-V1)<br>only | Exposed PAD on backside connects to GND.                    |

#### **■ MARK INFORMATION**

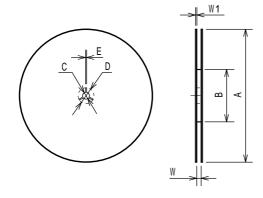

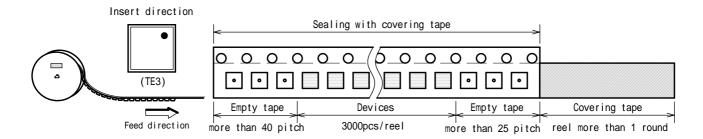

# DFN8 (ESON8-V1) NJU9103 KV1 (TE3) Part Number Package Taping Form Part Number Package Taping Form

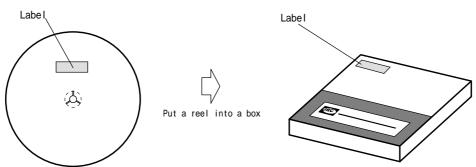

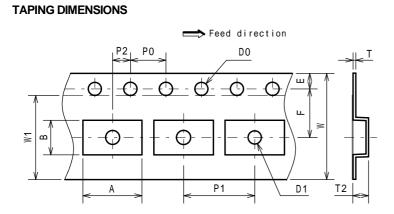

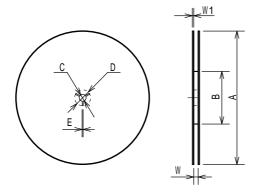

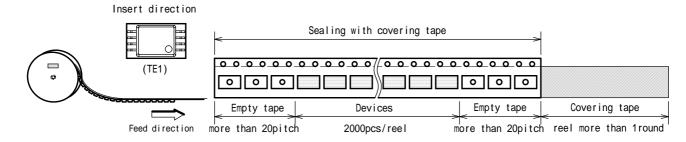

#### **■** ORDERING INFORMATION

| PART NUMBER | PACKAGE<br>OUTLINE | RoHS | Halogen-<br>Free | TERMINAL<br>FINISH | MARKING | WEIGHT (mg) | MOQ<br>(pcs) |

|-------------|--------------------|------|------------------|--------------------|---------|-------------|--------------|

| NJU9103KV1  | DFN8<br>(ESON8-V1) | yes  | yes              | Sn-2Bi             | 9103    | 7.2         | 3,000        |

| NJU9103V    | SSOP8              | yes  | yes              | Sn-2Bi             | 9103    | 42          | 2,000        |

#### **■ ABSOLUTE MAXIMUM RATINGS**

| PARAMETER                                | SYMBOL           | RATINGS                                                                                                      | UNIT |

|------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------|------|

| Power Supply Voltage                     | VDDabso          | 5 (4)                                                                                                        | V    |

| Power Dissipation (T <sub>a</sub> =25°C) | P <sub>D</sub>   | DFN8 (ESON8-V1): 580 <sup>(5)</sup> / 1785 <sup>(6)</sup><br>SSOP8 : 460 <sup>(5)</sup> / 595 <sup>(6)</sup> | mW   |

| Analog Input Voltage                     | V <sub>IN</sub>  | -0.3 to (VDD+0.3) (7)                                                                                        | V    |

| Operating Temperature Range              | Topr             | -40 to +125                                                                                                  | °C   |

| Storage Temperature Range                | T <sub>stg</sub> | -40 to +150                                                                                                  | °C   |

- (4) The difference between the absolute maximum power supply voltage and the operating power supply voltage is small. Please be careful so that the operating power supply voltage does not exceed the absolute maximum supply voltage by spike voltage.

- (5) Mounted on glass epoxy board.

- (114.3 x 76.2 x 1.57mm: based on EIA/JEDEC standard, 2Layers FR-4, with Exposed Pad)

- (6) Mounted on glass epoxy board

- (114.3 x 76.2 x 1.6mm: based on EIA/JEDEC standard, 4Layers FR-4, with Exposed Pad)

- (7) Input pin is connected to the clamp diode to the power supply pin. When the input signal exceeds the supply rails 0.3V or more (below the GND rail 0.3V or more), the input current must be limited to less than 10mA.

#### **■ RECOMMENDED OPERATING CONDITIONS**

| PARAMETER                   | SYMBOL           | RATINGS      | UNIT |

|-----------------------------|------------------|--------------|------|

| Power Supply Voltage        | VDD              | +2.7 to +3.6 | V    |

| Operating Temperature Range | Topr             | -40 to +125  | °C   |

| Storage Temperature Range   | T <sub>stg</sub> | -40 to +150  | °C   |

## ■ ELECTRICAL CHARACTERISTICS (Analog Input)

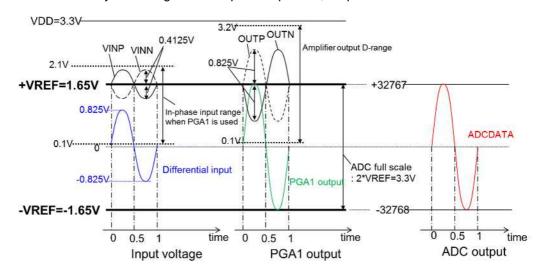

Unless otherwise specified, all limits ensured for  $T_a$ =+25°C, VDD=3.3V, GND=0V, VREF=0.5 x VDD, PGAIN1=PGAIN2=1, VCIN2=0.5 x VDD, DR=0.814ksps or 1.63ksps

| PARAMETER                             | SYMBOL       | TEST CONDITION                                         | MIN.       | TYP.                             | MAX.        | UNIT |

|---------------------------------------|--------------|--------------------------------------------------------|------------|----------------------------------|-------------|------|

| Analog Input 1 (PGA1=unused           | , PGA2=used, | PGAIN2=1 or 2 or 4)                                    |            |                                  |             |      |

| Differential Input Voltage<br>Range 1 | VDIN1        |                                                        | -          | ±VREF<br>/ (PGAIN2)              | -           | V    |

| Common Mode Input Voltage<br>Range 1  | VCIN1        |                                                        | GND        | -                                | VDD         | V    |

| La Harriera de                        | ZIN1         | FMOD = 1.25MHz<br>PGAIN2 = 1                           | -          | 400                              | 1           | k    |

| Input Impedance 1                     | ZIIVI        | FMOD = 1.25MHz<br>PGAIN2 = 2 or 4                      | -          | 200                              | -           | k    |

| Common Mode Rejection<br>Ratio 1      | CMRR1        | PGAIN2 = 1                                             | 70         | 90                               | ı           | dB   |

| Analog Input 2 (PGA1, 2=used          | PGAIN1=1 oi  | · 2 or 4 or 8 or 16 or 32 or 64                        | or 128, PC | GAIN2=1 or 2 or                  | or 4)       |      |

| Differential Input Voltage<br>Range2  | VDIN2        | PGAIN1≥2                                               | -          | (±VREF)<br>/(PGAIN1<br>x PGAIN2) | -           | V    |

| Common Mode Input Voltage<br>Range 2  | VCIN2        |                                                        | 0.1        | -                                | VDD<br>-1.2 | V    |

| Input Impedance 2                     | ZIN2         |                                                        | -          | 100                              | -           | M    |

|                                       |              | PGAIN1 = 2<br>PGAIN2 = 1                               | 40         | 60                               | -           | dB   |

| Common Mode Rejection<br>Ratio 2      | CMRR2        | PGAIN1 = 2<br>PGAIN2 = 1<br>CHOP= ON<br>DR = 0.407ksps | 70         | 90                               | ,           | dB   |

## ■ ELECTRICAL CHARACTERISTICS (Reference Voltage Input)

Unless otherwise specified, all limits ensured for T<sub>a</sub>=+25°C, VDD=3.3V, GND=0V

| PARAMETER          | SYMBOL | TEST CONDITION    | MIN.  | TYP. | MAX. | UNIT |

|--------------------|--------|-------------------|-------|------|------|------|

| Reference Voltage  | \/DEE  |                   | 0.5   |      | VDD  | V    |

|                    | VREF   |                   | x VDD | -    | VDD  | V    |

|                    | ZIN3   | FMOD = 1.25MHz    |       | 100  |      | le.  |

| lanut langadanaa 2 |        | PGAIN2 = 1  or  2 | -     | 180  | -    | K    |

| Input Impedance 3  |        | FMOD = 1.25MHz    |       | 000  |      | le.  |

|                    |        | PGAIN2 = 4        | -     | 300  | -    | K    |

## ■ ELECTRICAL CHARACTERISTICS (Internal Oscillator)

Unless otherwise specified, all limits ensured for T<sub>a</sub>=+25°C, VDD=3.3V, GND=0V

| • •           |        |                |      |      |      |      |

|---------------|--------|----------------|------|------|------|------|

| PARAMETER     | SYMBOL | TEST CONDITION | MIN. | TYP. | MAX. | UNIT |

| OSC Frequency | FOSC   |                | 1.75 | 2.5  | 3.25 | MHz  |

## **■ ELECTRICAL CHARACTERISTICS (Programmable Gain Amplifier)**

Unless otherwise specified, all limits ensured for T<sub>a</sub>=+25°C, VDD=3.3V, GND=0V

| PARAMETER | SYMBOL | TEST CONDITION | MIN. | TYP.                               | MAX. | UNIT |

|-----------|--------|----------------|------|------------------------------------|------|------|

| PGA1 Gain | PGAIN1 |                | -    | 1, 2, 4, 8,<br>16, 32, 64,<br>128, | 1    | V/V  |

| PGA2 Gain | PGAIN2 |                | -    | 1, 2, 4                            | 1    | V/V  |

## ■ ELECTRICAL CHARACTERISTICS (Analog to Digital Convertor)

Unless otherwise specified, all limits ensured for  $T_a=+25$ °C, VDD=3.3V, GND=0V, VREF=0.5 x VDD, PGAIN1=PGAIN2=1, VCIN2=0.5 x VDD

| PARAMETER                      | SYMBOL         | TEST CONDITION                                              | MIN.   | TYP.                        | MAX.  | UNIT |

|--------------------------------|----------------|-------------------------------------------------------------|--------|-----------------------------|-------|------|

| Resolution                     | N              | No missing codes <sup>(8)</sup>                             | 16     |                             |       | Bit  |

| Data Rate                      | DR             | Single Conversion <sup>(9)</sup>                            | 0.814k | 0.814k, 1.63k, 3.26k, 6.51k |       |      |

| Clock Frequency                | FMOD<br>(MDCK) | FMOD = FOSC/2                                               | 0.875  | 1.25                        | 1.625 | MHz  |

| Integral Non Linearity         | INL            | best-fit-line method <sup>(10)</sup> VREF = VDD  PGAIN1 = 2 | -      | ±30                         | ±60   | ppm  |

|                                |                | PGAIN1 = 128<br>Input-Referred Offset                       | -      | 200                         | -     | μV   |

| Offset Error                   | OE             | PGAIN1 = 128<br>Input-Referred Offset<br>CHOP=ON            | -      | <del>+</del> 2              | ±10   | μV   |

| Onio Emp                       | 05             | SSOP8 PGAIN1 = 128 DR = 3.26ksps                            | 1.0    | 2.5                         | 4.0   | 0/   |

| Gain Error                     | GE             | DFN8 (ESON8-V1) PGAIN1 = 128 DR = 3.26ksps                  | 0.5    | 2.0                         | 3.5   | %    |

| Noise Free Bit <sup>(11)</sup> | NED            | VDIN2 = 0V<br>VREF = 3.3V<br>DR = 0.814ksps <sup>(8)</sup>  | 14     | 15                          | -     | Bit  |

|                                | NFB            | VDIN2 = 0V<br>VREF = 3.3V<br>DR = 1.63ksps <sup>(8)</sup>   | 13     | 14                          | -     | Bit  |

<sup>(8)</sup> This parameter is not production tested, please refer Typical Characteristics.

<sup>(9)</sup> There is no latency by one settling behavior.

<sup>(10)</sup> Guaranteed by design evaluation and several points test

<sup>(11)</sup> NFB represents the ADC output code variations  $6.6\sigma$  with the differential input shorted.

## ■ ELECTRICAL CHARACTERISTICS (Power Supply / Supply Current)

Unless otherwise specified, all limits ensured for  $T_a$ =+25°C, VDD=3.3V, GND=0V

| PARAMETER            | SYMBOL     | TEST CONDITION  | MIN.  | TYP.  | MAX.  | UNIT |

|----------------------|------------|-----------------|-------|-------|-------|------|

| Power Supply Voltage | VDD        |                 | 2.7   | 3.3   | 3.6   | V    |

| Supply Current 1     | IDD        | PGA OFF         | 1.65  | 2.3   | 3.0   | mA   |

|                      | טטו        | PGA ON          | 3.0   | 4.0   | 5.0   | mA   |

| Supply Current 2     | $IDD_{pd}$ | Power Down Mode | 12.75 | 17.00 | 21.25 | μA   |

## ■ ELECTRICAL CHARACTERISTICS (Digital I/Os)

Unless otherwise specified, all limits ensured for T<sub>a</sub>=+25°C, VDD=3.3V, GND=0V

| PARAMETER                              | SYMBOL            | TEST CONDITION            | MIN.         | TYP. | MAX.         | UNIT |

|----------------------------------------|-------------------|---------------------------|--------------|------|--------------|------|

| Positive-going input threshold voltage | V <sub>th</sub> + |                           | -            | 1.6  | -            | V    |

| Negative-going input threshold voltage | V <sub>th</sub> - |                           | -            | 1.2  | -            | V    |

| Input voltage hysteresis               | V <sub>hyst</sub> | VDD = 3.0V                | -            | 280  | -            | mV   |

| High-level input voltage               | V <sub>ih</sub>   |                           | 0.7<br>x VDD | -    | -            | V    |

| Low-level input voltage                | Vil               |                           | -            | -    | 0.3<br>x VDD | V    |

| High-level output voltage              | V <sub>oh</sub>   | I <sub>oh</sub> max.= 6mA | 0.8<br>x VDD | -    | -            | V    |

| Low-level output voltage               | Vol               | l₀ max.= 6mA              | -            | -    | 0.4          | V    |

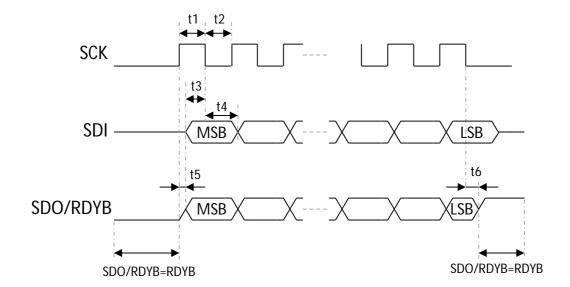

## ■ ELECTRICAL CHARACTERISTICS (Serial Peripheral Interface)

| PARAMETER                         | SYMBOL            | MIN. | TYP. | MAX. | UNIT |

|-----------------------------------|-------------------|------|------|------|------|

| SPI clock frequency               | F <sub>sck</sub>  | -    | -    | 10   | MHz  |

| High period of the SCK clock      | t1                | 45   | -    | -    | ns   |

| Low period of the SCK clock       | t2                | 45   | -    | -    | ns   |

| SDI input data setup time         | t3                | 5    | -    | -    | ns   |

| SDI input data hold time          | t4                | 5    | -    | -    | ns   |

| SDO / RDYB output data setup time | t5                | 0    | -    | 40   | ns   |

| SDO / RDYB output data hold time  | t6                | 10   | -    | 50   | ns   |

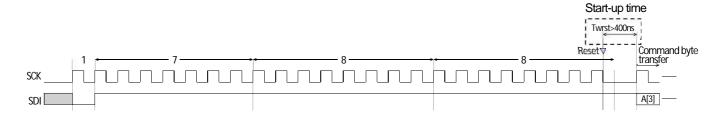

| Reset time                        | t <sub>rstw</sub> | -    | -    | 400  | ns   |

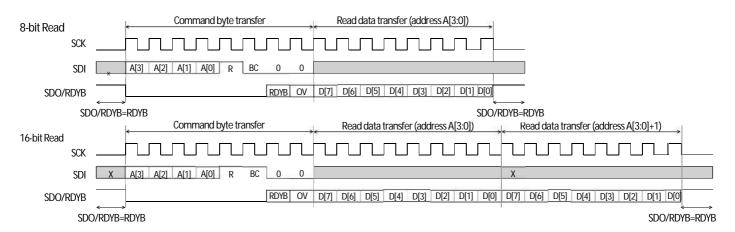

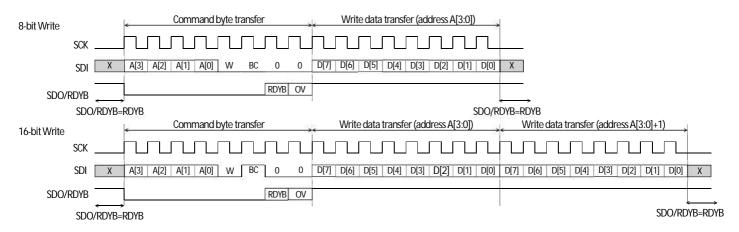

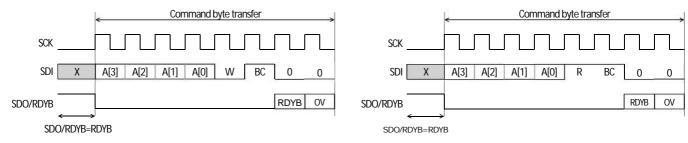

- The SPI of AC timing is shown in the figure below. At the maximum, it is the communication of 10Mbps.

- Load of SDO / RDB terminal is assumed to 40pF

- CSB terminal (chip select terminal) is fixed at a low level inside the chip.

- In order to connect a plurality of NJU9103, it requires SPI bus that is equally the number of NJU9103.

#### **■ REGISTER DESCRIPTION**

NJU9103 has register (list shown below) which can access it through SPI bus.

| REGISTER | REGISTER |                                  |                       |       | BIT          |         |     |              |         |

|----------|----------|----------------------------------|-----------------------|-------|--------------|---------|-----|--------------|---------|

| ADDRESS  | NAME     | [7]                              | [6]                   | [5]   | [4]          | [3]     | [2] | [1]          | [0]     |

| 0x0      | CTRL     | RDYB OV / CHSEL [1:0] MODE [3:0] |                       |       |              |         |     |              |         |

| 0x1      | ADCDATA0 |                                  |                       |       | ADCDATA      | (15:8]  |     |              |         |

| 0x2      | ADCDATA1 |                                  |                       |       | ADCDATA      | A [7:0] |     |              |         |

| 0x3      | PGACONF  | =                                | -                     | PGA2G | AIN [1:0]    | PGA1EN  |     | PGA1GAIN [2: | 0]      |

| 0x4      | CLKCONF  | -                                | -                     | CLKD  | IV [1:0]     | -       |     | OSR [2:0]    |         |

| 0x5      | DACCONF  | -                                | CALDACEN CALDAC [4:0] |       |              |         |     |              |         |

| 0x6      | OPTION0  |                                  |                       |       | CHIPID [6:0] |         |     |              | AUTOSLP |

| 0x7      | Not used |                                  |                       |       | -            |         |     |              |         |

| 0x8      | GAIN0    |                                  |                       |       | GAIN [23     | 3:16]   |     |              |         |

| 0x9      | GAIN1    |                                  |                       |       | GAIN [1      | 5:8]    |     |              |         |

| 0xA      | GAIN2    |                                  |                       |       | GAIN [7      | 7:0]    |     |              |         |

| 0xB      | OFFSET0  |                                  |                       |       | OFFSET [     | 23:16]  |     |              |         |

| 0xC      | OFFSET1  |                                  | OFFSET [15:8]         |       |              |         |     |              |         |

| 0xD      | OFFSET2  |                                  | OFFSET [7:0]          |       |              |         |     |              |         |

| 0xE      | Not used |                                  | -                     |       |              |         |     |              |         |

| 0xF      | Not used |                                  |                       |       | =            |         |     |              |         |

## < View of the register table>

|          | REGISTER NAME |     |     |     |     |     |     |     |

|----------|---------------|-----|-----|-----|-----|-----|-----|-----|

| BIT      | [7]           | [6] | [5] | [4] | [3] | [2] | [1] | [0] |

| BIT NAME |               |     |     |     |     |     |     |     |

| R/W      |               |     |     |     |     |     |     |     |

| RESET    |               |     |     |     |     |     |     |     |

R/W: Bit of attribute (Write or Read)

- R (Read Only) : Read only

- W (Write Only) : Write only (At the time of read, return "0".)

- RW (Read Write) : Read & Write

Reset: Reset value in register

Set to the reset value by SPI reset command and power-on.

## **■ EVERY REGISTER DESCRIPTION**

**CTRL Register** Register Address: 0x0

|            |      | <u> </u> |             |      |            |     |            |     |  |  |

|------------|------|----------|-------------|------|------------|-----|------------|-----|--|--|

|            |      |          |             | CTRL |            |     |            |     |  |  |

| BIT        | [7]  | [6]      | [5] [4]     |      | [3]        | [2] | [1]        | [0] |  |  |

| BIT NAME   | RDYB | OV -     |             | -    | MODE (3:0) |     |            |     |  |  |

| DII NAIVIE | מוטא |          | CHSEL [2:0] |      | MODE [3:0] |     |            |     |  |  |

| R/W        | R    | R/W      | R           | W    | RW         |     |            |     |  |  |

| RESET      | 1    | 0        | 0:          | x0   |            | 0>  | <b>(</b> 0 |     |  |  |

| BIT   | BIT NAME      | FUNCTION                                                                                |

|-------|---------------|-----------------------------------------------------------------------------------------|

|       |               | Data Ready Flag. When conversion data is updated, this bit is set to "0".               |

|       |               | When "ADCDATAO" is read, this bit is set to "1".                                        |

| [7]   | [7] RDYB      |                                                                                         |

|       |               | 0: Ready                                                                                |

|       |               | 1: Not ready                                                                            |

|       |               | Overflow flag. When conversion data is overflow, this bit is set to "1".                |

|       |               | When "ADCDATA0" is read, this bit is set to "1".                                        |

| [6]   | OV            |                                                                                         |

| [O]   |               | 0: Valid                                                                                |

|       |               | 1: Overflow (Data is invalid)                                                           |

|       | CHSEL [2:0]   | Analog input channel setting.                                                           |

| [5:4] | Of IOCE [2.0] | Please refer to Table 1 for details.                                                    |

| [3:0] | MODE          | Operation mode setting. When this bit is read, returns the current configuration state. |

| [3:0] | IVIODE        | Please refer to Table 2 for details.                                                    |

Table 1 CHSEL [2:0]

| CHSEL [2:0] | Positive | Negative            |

|-------------|----------|---------------------|

| 0x0         | VINP     | VINN                |

| 0x1         | Not us   | sed <sup>(12)</sup> |

| 0x2         | VINP     | GND                 |

| 0x3         | VINN     | GND                 |

| 0x4         | VREF     | GND                 |

| 0x5         | GND      | GND                 |

| 0x6         | VINN     | VINN                |

| 0x7         | Not us   | sed <sup>(12)</sup> |

<sup>(12)</sup> Please do not absolutely use the "Not used" code. It will be the cause of failure.

Table 2 MODE [3:0]

| Table 2    | INODE [3.0]                            | ,                                                                                                                                                                                                                                                                                                                                                 |

|------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODE [3:0] | Operation                              | Processing                                                                                                                                                                                                                                                                                                                                        |

| 0x0        | idle                                   | Conversion operation waiting state                                                                                                                                                                                                                                                                                                                |

| 0x1        | Not used <sup>(13)</sup>               | -                                                                                                                                                                                                                                                                                                                                                 |

| 0x2        | Single conversion                      | Convert once the input channel that is selected in the CHSEL [2:0].  After the conversion, the operation is "idle (0x0)" state.  Using the value of the "OFFSET0, 1, 2" register.                                                                                                                                                                 |

| 0x3        | Continuous conversion                  | Convert continuous the input channel that is selected in the CHSEL[2:0].  Until the operation is set to "idle (0x0)", conversion will continue.  Using the value of the "OFFSETO, 1, 2" register.                                                                                                                                                 |

| 0x4        | Single conversion<br>+ CHOP            | This is the same as "Single conversion (0x2)", but the data rate is 1/2.  Not using the value of the "OFFSET0, 1, 2" register.                                                                                                                                                                                                                    |

| 0x5        | Continuous conversion + CHOP           | This is the same as "Continuous conversion (0x3)", but the data rate is 1/3. Not using the value of the "OFFSET0, 1, 2" register.                                                                                                                                                                                                                 |

| 0x6        | Not used(13)                           | -                                                                                                                                                                                                                                                                                                                                                 |

| 0x7        | Not used <sup>(13)</sup>               | -                                                                                                                                                                                                                                                                                                                                                 |

| 0x8        | Calibration ADC offset                 | When you run this command, the following will be processed automatically.  - PGA1 turn off, PGA2 gain is set to "x1".  - Input is fixed to GND/GND internally, ADC offset will be calibrated.  - Coefficient is stored in the offset register. In this case, the CHSEL [2:0] setting is invalid.                                                  |

| 0x9        | Calibration ADC gain                   | When you run this command, the following will be processed automatically.  - PGA1 turn off, PGA2 gain is set to "x1".  - Input is fixed to VREF/GND internally, ADC gain will be calibrated.  - Coefficient is stored in the gain register.  In this case, the CHSEL [2:0] setting is invalid.                                                    |

| 0xA        | Calibration PGA offset <sup>(14)</sup> | When you run this command, the following will be processed automatically.  However, before the execution of this command to set the PGA1 / PGA2 gain.  - Input is fixed to VNN/VNN internally, PGA offset will be calibrated.  - Coefficient is stored in the offset register.  In this case, the CHSEL [2:0] setting is invalid.                 |

| 0xB        | Not used <sup>(13)</sup>               | -                                                                                                                                                                                                                                                                                                                                                 |

| 0xC        | Calibration system offset              | This command is calibrated in a state in which to connect the sensor.  When you run this command, the following will be processed automatically.  However, before the execution of this command to set the input channel.  - Input is selected by CHSEL [2:0], system offset will be calibrated.  - Coefficient is stored in the offset register. |

| 0xD        | Calibration system gain                | This command is calibrated in a state in which to connect the sensor.  When you run this command, the following will be processed automatically.  However, before the execution of this command to set the input channel.  - Input is selected by CHSEL [2:0], system gain will be calibrated.  - Coefficient is stored in the gain register.     |

| 0xE        | Not used <sup>(13)</sup>               | -                                                                                                                                                                                                                                                                                                                                                 |

| 0xF        | Boot                                   | Read-only. It shows the state from the reset to change to idle (0x0).  After the initial setting, automatically shifts to the "idle (0x0)".                                                                                                                                                                                                       |

<sup>(13)</sup> Please do not absolutely use the "Not used" code. It will be the cause of failure.

<sup>(14)</sup> Before the commands are executed, please set PGA1/2 of the gain to PGACONF register.

#### ADCDATA0 / ADCDATA1 Register

| ADCDATA0 / ADCDATA1 Register |     |                                 |  |      |       |     | Register Address: 0x1 / 0x2 |      |          |     |     |     |     |     |  |  |

|------------------------------|-----|---------------------------------|--|------|-------|-----|-----------------------------|------|----------|-----|-----|-----|-----|-----|--|--|

|                              |     |                                 |  | ADCD | OATA0 |     |                             |      | ADCDATA1 |     |     |     |     |     |  |  |

|                              |     | Register Address: 0x1           |  |      |       |     | Register Address: 0x2       |      |          |     |     |     |     |     |  |  |

| BIT                          | [7] | [7] [6] [5] [4] [3] [2] [1] [0] |  |      |       | [0] | [7]                         | [6]  | [5]      | [4] | [3] | [2] | [1] | [0] |  |  |

| BIT NAME                     |     |                                 |  |      |       |     | Α                           | DCDA | TA [15:0 | 0]  |     |     |     |     |  |  |

| R/W                          |     |                                 |  |      |       |     |                             | F    | ₹        |     |     |     |     |     |  |  |

| RESET                        |     |                                 |  |      |       |     |                             |      | -        |     |     |     |     |     |  |  |

| BIT                 | BIT NAME       | FUNCTION                                                                    |

|---------------------|----------------|-----------------------------------------------------------------------------|

|                     |                | Store the converted data of the ADC. <sup>(15)</sup>                        |

| 4 DCD 4 T 4 0 [7:0] |                | Conversion data is expressed as a signed 16-bit.                            |

| ADCDATA0 [7:0]      | ADCDATA [45:0] | - Negative full-scale voltage is 0x8000                                     |

| +<br>^DCD^T^1(7:0)  | ADCDATA [15:0] | - When the input voltage is zero 0x0000                                     |

| ADCDATA1 [7:0]      |                | - Positive full-scale voltage will be 0x7FFF. (in decimal -32768 to +32767) |

|                     |                | Please be sure to perform a read in order of ADCDATA0, ADCDATA1.            |

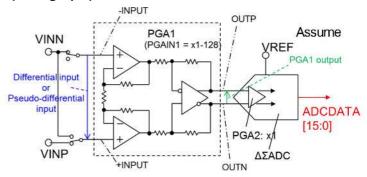

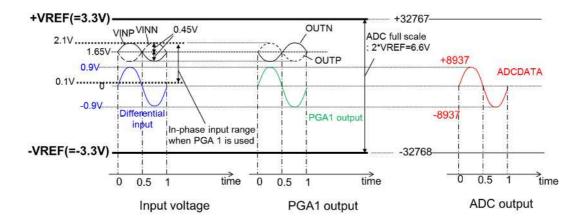

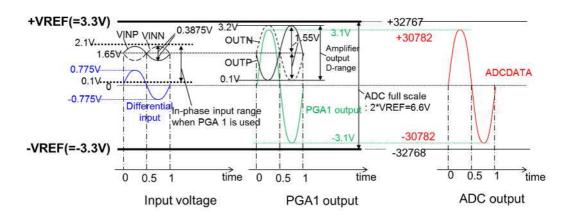

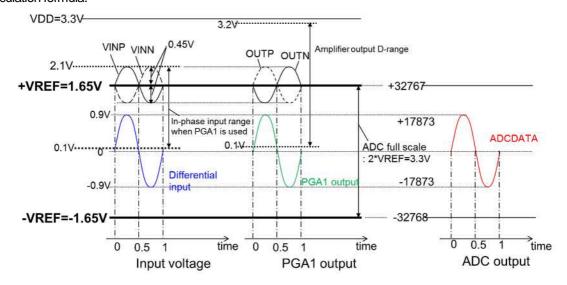

(15) Relationship of conversion data ADCDATA and the analog input voltage Vin is as the following equation. (It assumed that the offset error and gain error are zero.)

$$ADCDATA = \frac{V_{in}}{2 \times VREF} \times PGAIN1 \times PGAIN2 \times 2^{16} = \frac{V_{in}}{VREF} \times PGAIN1 \times PGAIN2 \times 2^{15}$$

## **PGACONF** Register

| PGACONF R | PGACONF Register Address: 0x3 |     |      |       |        |          |     |     |  |  |

|-----------|-------------------------------|-----|------|-------|--------|----------|-----|-----|--|--|

|           | PGACONF                       |     |      |       |        |          |     |     |  |  |

| BIT       | [7]                           | [6] | [5]  | [4]   | [3]    | [2]      | [1] | [0] |  |  |

| BIT NAME  | -                             | -   | PGA2 | 2GAIN | PGA1EN | PGA1GAIN |     |     |  |  |

| R/W       | -                             | -   | RW   |       | RW     | RW       |     |     |  |  |

| RESET     | -                             | -   | 0x0  |       | 0      | 0x0      |     |     |  |  |

| BIT   | BIT NAME | FUNCTION                                                                                    |

|-------|----------|---------------------------------------------------------------------------------------------|

| [5:4] | PGA2GAIN | Gain setting of PGA2.  0x0: x1 0x1: x2 0x2: x4 0x3: Not used(16)                            |

| [3]   | PGA1EN   | Setting ON / OFF of PGA1.  0: OFF  1: ON                                                    |

| [2:0] | PGA1GAIN | Gain setting of PGA1.  0x0: x1 0x1: x2 0x2: x4 0x3: x8 0x4: x16 0x5: x32 0x6: x64 0x7: x128 |

<sup>(16)</sup> Please do not absolutely use the "Not used" code. It will be the cause of failure.

Register Address: 0x4

#### **CLKCONF** Register

|          | CLKCONF |     |                     |      |   |     |     |  |  |

|----------|---------|-----|---------------------|------|---|-----|-----|--|--|

| BIT      | [7]     | [6] | [5] [4] [3] [2] [1] |      |   |     |     |  |  |

| BIT NAME | -       | -   | CLk                 | (DIV | - | OSR |     |  |  |

| R/W      | -       | -   | R'                  | W    | - | RW  |     |  |  |

| RESET    | -       | -   | 0:                  | к0   | - |     | 0x3 |  |  |

| BIT   | BIT NAME   | FUNCTION                                                                                              |

|-------|------------|-------------------------------------------------------------------------------------------------------|

|       |            | Setting of the ADC operating clock frequency (FMOD). FOSC is the operating clock of the internal OSC. |

| [5:4] | CLKDIV(17) | 0x0: FOSC/2                                                                                           |

|       |            | 0x1: FOSC/4                                                                                           |

|       |            | 0x2: FOSC/8                                                                                           |

|       |            | 0x3: FOSC/16                                                                                          |

|       |            | Setting of the oversampling ratio of the digital filter                                               |

|       |            | 0x0: 64                                                                                               |

| [2:0] | OSR        | 0x1: 128                                                                                              |

|       |            | 0x2: 256                                                                                              |

|       |            | 0x3: 512                                                                                              |

|       |            | 0x4 to 0x7: Not used <sup>(18)</sup>                                                                  |

(17) Data rate is derived by the following equation. It will be the data rate of a single conversion.

$$DR = F_{OSC} \times \frac{1}{OSR} \times \frac{1}{2^{(CLKDIV+1)}} \times \frac{1}{3}$$

If FOSC is 2.5MHz of (TYP.), Conversion data rate will be set in the table below.

|     |                           | Date Rate [sps] |             |             |  |  |  |  |  |  |  |  |

|-----|---------------------------|-----------------|-------------|-------------|--|--|--|--|--|--|--|--|

| OSR | CLKDIV=0 (Recommendation) | CLKDIV=1(*)     | CLKDIV=2(*) | CLKDIV=3(*) |  |  |  |  |  |  |  |  |

| 512 | 0.814k                    | 0.407k          | 0.204k      | 0.102k      |  |  |  |  |  |  |  |  |

| 256 | 1.63k                     | 0.814k          | 0.407k      | 0.204k      |  |  |  |  |  |  |  |  |

| 128 | 3.26k                     | 1.63k           | 0.814k      | 0.407k      |  |  |  |  |  |  |  |  |

| 64  | 6.51k                     | 3.26k           | 1.63k       | 0.814k      |  |  |  |  |  |  |  |  |

(\*) Design guarantee.

(18) Please do not absolutely use the "Not used" code. It will be the cause of failure.

Register Address: 0x5

## **DACCONF** Register

|          | DACCONF |     |          |              |    |      |  |  |  |  |  |  |  |

|----------|---------|-----|----------|--------------|----|------|--|--|--|--|--|--|--|

| BIT      | [7]     | [6] |          |              |    |      |  |  |  |  |  |  |  |

| BIT NAME | -       | -   | CALDACEN | CALDAC [4:0] |    |      |  |  |  |  |  |  |  |

| R/W      | -       | -   | RW       |              | RW |      |  |  |  |  |  |  |  |

| RESET    | -       | -   | 0        |              |    | 0x00 |  |  |  |  |  |  |  |

| BIT   | BIT NAME               | FUNCTION                                                                                |

|-------|------------------------|-----------------------------------------------------------------------------------------|

|       |                        | Setting ON/OFF of DAC                                                                   |

| [5]   | CALDACEN               | 0: OFF (Power down)                                                                     |

|       |                        | 1: ON                                                                                   |

| [4.0] | CAL DAC(19)            | The sensor offset is corrected to add or subtract the DAC voltage from the output PGA1. |

| [4:0] | CALDAC <sup>(19)</sup> | CALDAC is a signed 5-bit code, MSB is the sign bit.                                     |

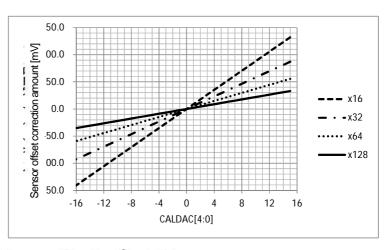

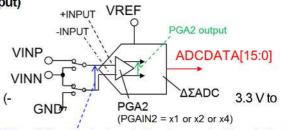

#### (19) NJU9103 contains internal calibration DAC.

When the gain of NJU9103 is large and the offset of sensor is 10mV, the data conversion does not work correctly by the constraints of the D-range of the analog circuit. To correct this, DAC will generate a voltage opposite to offset voltage of the sensor.

A simplified block diagram of the input section of the NJU9103 is shown below.

The correction range and resolution (voltage step) of sensor are changed by PGA1 gain.

It can be derived by the following equation.

"Sensor offset correction value" = "Resolution" x CALDAC[4:0]

(Note) Design assurance at VDD = 3.3V.

The variation of the resolution (error) is about  $\pm$  15%.

| PGAIN1 | Resolution[mV] |

|--------|----------------|

| x16    | 8.8            |

| x32    | 5.8            |

| x64    | 3.7            |

| x128   | 2.2            |

## **OPTION0** Register

| OPTION0 Register Register Address: |                       |                             |  |      |  |  |  |   |  |  |  |  |

|------------------------------------|-----------------------|-----------------------------|--|------|--|--|--|---|--|--|--|--|

| OPTION0                            |                       |                             |  |      |  |  |  |   |  |  |  |  |

| BIT                                | [7]                   | [7] [6] [5] [4] [3] [2] [1] |  |      |  |  |  |   |  |  |  |  |

| BIT NAME                           | BIT NAME CHIPID [6:0] |                             |  |      |  |  |  |   |  |  |  |  |

| R/W                                |                       | R                           |  |      |  |  |  |   |  |  |  |  |

| RESET                              |                       |                             |  | 0x00 |  |  |  | 0 |  |  |  |  |

| BIT   | BIT NAME | FUNCTION                                                                                                                                                                                                          |

|-------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:1] | CHIPID   | Used to identify the chip.                                                                                                                                                                                        |

| [0]   | AUTOSLP  | Wen MODE[3:0] is idle (0x0), set to ON / OFF of analog block  0: ON (Wait)  1: OFF (Power down)  When the customer change AUTOSLP from 1to 0, conversion start is necessary to start-up time of the analog block. |

## GAIN0/GAIN1/GAIN2 Register

Register Address: 0x8, 0x9, 0xA

|          | GAIN0                 | GAIN1                 | GAIN2                 |  |  |  |  |  |  |  |  |  |  |

|----------|-----------------------|-----------------------|-----------------------|--|--|--|--|--|--|--|--|--|--|

|          | Register Address: 0x8 | Register Address: 0x9 | Register Address: 0xA |  |  |  |  |  |  |  |  |  |  |

| BIT      | 7 6 5 4 3 2 1 0       | 7 6 5 4 3 2 1 0       | 7 6 5 4 3 2 1 0       |  |  |  |  |  |  |  |  |  |  |

| BIT NAME |                       | GAIN [23:0]           |                       |  |  |  |  |  |  |  |  |  |  |

| R/W      |                       | RW                    |                       |  |  |  |  |  |  |  |  |  |  |

| RESET    | 0x01                  | 0x00                  | 0x00                  |  |  |  |  |  |  |  |  |  |  |

| BIT                             | BIT NAME    | FUNCTION                                                                                                                                           |

|---------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| GAIN0 [7:0]<br>+                |             | Gain coefficient derived in gain calibration or the external writing gain coefficient.  18-bit unsigned coefficient, GAIN [23:18] is always "0".   |

| GAIN1 [7:0]<br>+<br>GAIN2 [7:0] | GAIN [23:0] | The customer can do the external writing gain coefficient, when internal clock is active only.  Please set to "0" AUTOSLP bit of OPTION0 register. |

Register Address: 0xB, 0xC, 0xD

## OFFSET0 / OFFSET1 / OFFSET2 Register

|          |                       | OFFSET0       |  |     |    |   | OFFSET1               |   |   |   |   | OFFSET2               |    |   |   |   |      |   |   |   |   |   |

|----------|-----------------------|---------------|--|-----|----|---|-----------------------|---|---|---|---|-----------------------|----|---|---|---|------|---|---|---|---|---|

|          | Register Address: 0xB |               |  |     |    |   | Register Address: 0xC |   |   |   |   | Register Address: 0xD |    |   |   |   |      |   |   |   |   |   |

| BIT      | 7 6 5 4 3 2 1 0       |               |  |     |    | 0 | 7                     | 6 | 5 | 4 | 3 | 2                     | 1  | 0 | 7 | 6 | 5    | 4 | 3 | 2 | 1 | 0 |

| BIT NAME |                       | OFFSET [23:0] |  |     |    |   |                       |   |   |   |   |                       |    |   |   |   |      |   |   |   |   |   |

| R/W      |                       | RW            |  |     |    |   |                       |   |   |   |   |                       |    |   |   |   |      |   |   |   |   |   |

| RESET    |                       |               |  | 0x0 | 00 |   |                       |   |   |   |   | 0x                    | 00 |   |   |   | 0x00 |   |   |   |   |   |

| BIT                                                       | BIT NAME      | FUNSTION                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OFFSET0 [7:0]<br>+<br>OFFSET1 [7:0]<br>+<br>OFFSET2 [7:0] | OFFSET [23:0] | Offset coefficient derived in offset calibration or the external writing offset coefficient.  20-bit signed coefficient, OFFSET [23:20] is sign-extended value. (20)  The customer can do the external writing offset coefficient, when internal clock is active only.  Please set to "0" AUTOSLP bit of OPTION0 register. |

(20) Sign-extended: If the sign is (-) fill the 1 in the free space. If the sign is (+) fill the "0" in the free space

- In the case of -4 in decimal 8- bit is "11111100".

16-bit sign extension is "11111111 1111100".

- In the case of +4 in decimel 8-bit is "00000100"

16-bit sign extension is "00000000 00000100"

#### ■ APPLICATION NOTE / GLOSSARY

#### ■ Power up sequence

When the power supply is started, the reset cancellation is valid.

After a reset cancellation, the circuit will start operating.

The time from the reset cancellation to the operation start state is required waiting time of about 30µs.

(The rise time of power signal is not included.)

## ■ Effective resolution, Noise Free Bit (NFB)

Data Rate (DR) is speed at the time of single conversion (1 settling).

Output code variation  $\sigma$  is the effective resolution in the VINP and VINN connected to VDD/2, 6.6 $\sigma$  is the NFB.

#### < Condition >

- FMOD=1.25MHz

- VDD=3.3V, GND=0V

- VREF=3.3V

- Differential input

- Ta=+25°C

## DR vs. Effective resolution (Unit: bit)

| DR     | PGA<br>OFF |      | PGA ON |      |      |      |      |      |      |      |      |  |  |  |

|--------|------------|------|--------|------|------|------|------|------|------|------|------|--|--|--|

| [sps]  |            | x1   | x2     | x4   | x8   | X16  | x32  | x64  | x128 | x256 | x512 |  |  |  |

| 0.814k | 16         | 16   | 16     | 16   | 16   | 16   | 16   | 16   | 15.5 | 15   | 14   |  |  |  |

| 1.63k  | 16         | 16   | 16     | 16   | 16   | 16   | 16   | 16   | 15   | 14   | 13   |  |  |  |

| 3.26k  | 15.5       | 15.5 | 15.5   | 15.5 | 15.5 | 15.5 | 15.5 | 15.5 | 14.5 | 13.5 | 12.5 |  |  |  |

| 6.51k  | 14         | 14   | 14     | 14   | 14   | 14   | 14   | 14   | 13.5 | 13   | 11.5 |  |  |  |

## DR vs. NFB (Unit: bit)

|        | PGA |    | PGA ON |    |      |      |      |      |      |      |      |  |  |  |

|--------|-----|----|--------|----|------|------|------|------|------|------|------|--|--|--|

|        | OFF | x1 | x2     | x4 | x8   | x16  | x32  | x64  | x128 | x256 | x512 |  |  |  |

| 0.814k | 15  | 15 | 15     | 15 | 14.5 | 14.5 | 14.5 | 13.5 | 13   | 12   | 11   |  |  |  |

| 1.63k  | 14  | 14 | 14     | 14 | 14   | 14   | 14   | 13.5 | 12.5 | 11.5 | 10.5 |  |  |  |

| 3.26k  | 13  | 13 | 13     | 13 | 13   | 13   | 13   | 12.5 | 12   | 11   | 10   |  |  |  |

| 6.51k  | 11  | 11 | 11     | 11 | 11   | 11   | 11   | 11   | 11   | 10   | 9    |  |  |  |

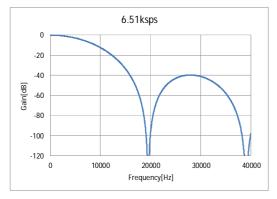

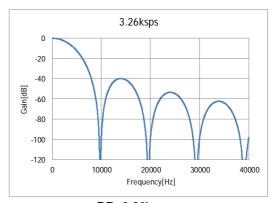

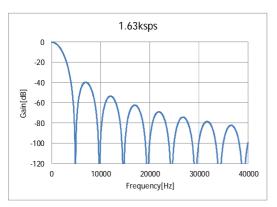

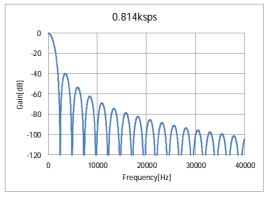

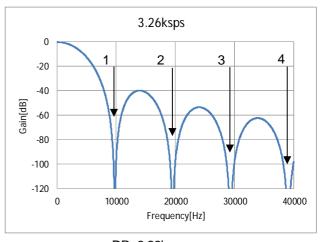

#### ■ Digital filter frequency characteristic

The output of the  $\Delta\Sigma$  modulator is converted to a digital value of high resolution by a digital filter (third-order Sinc filter). Frequency characteristics will change depending on the data rate.

When the conversion data rate (DR) is 6.51ksps, 3.26ksps, 1.63ksps, 0.814ksps, frequency characteristics of the digital filter is shown below. Characteristic is the case of FMOD=1.25MHz.

DR=6.51ksps

DR=3.26ksps

DR=1.63ksps

DR=0.814ksps

It has a first notch in the frequency of the data rate x 3.

Or later, it has a notch to the integer multiple of the position. (21)

(e.x.) In the case 3.26ksps (Figure of right)

Position of the notch

- 1. 9.8kHz (3.26kHz x 3 x 1)

- 2. 19.6kHz (3.26kHz x 3 x 2)

- 3. 29.3kHz (3.26kHz x 3 x 3)

- 4. 39.1kHz (3.26kHz x 3 x 4)

. (N) 3.26kHz x 3 x N (N is an integer)

DR=3.26ksps

(21) Position of the notch varies in proportion to the frequency of the FMOD FMOD is ±25% variation. Position of the notch is likely to vary ±25% from the above figure.

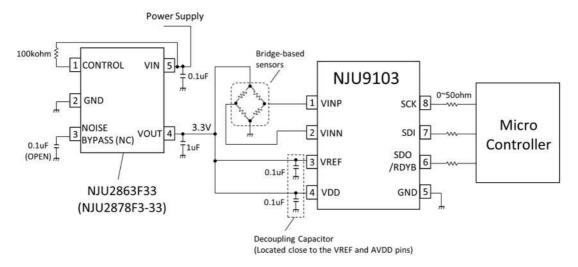

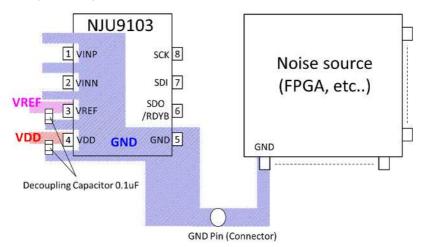

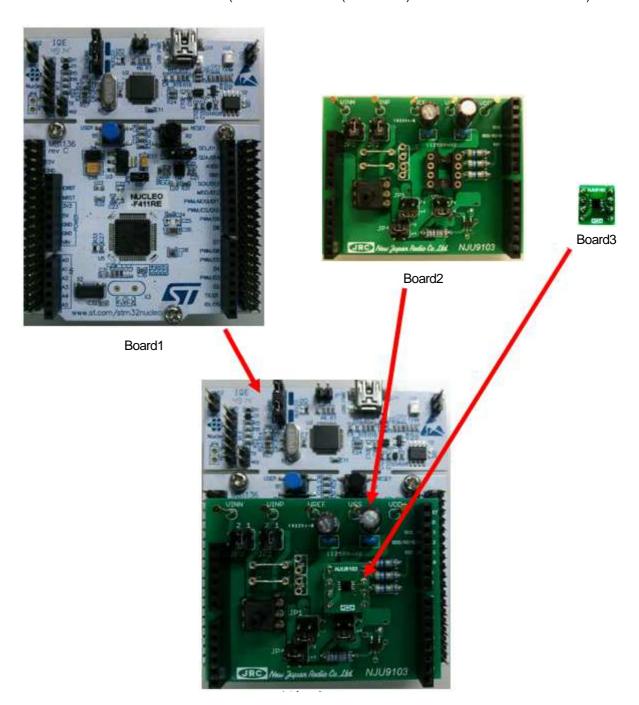

## **■ System Example**

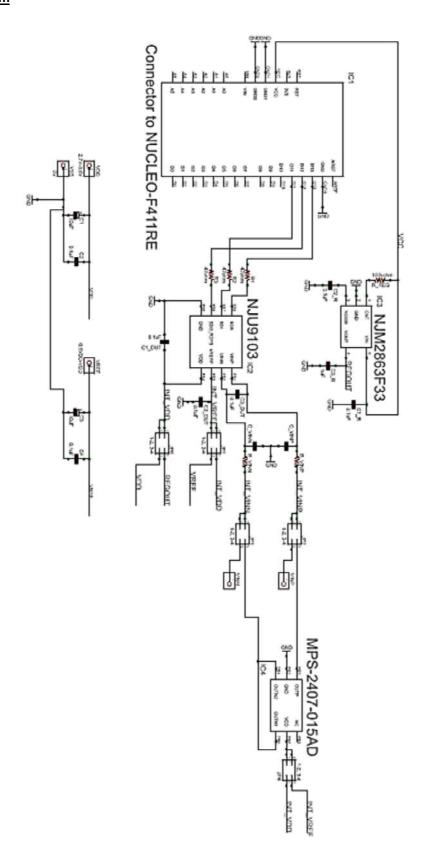

An example of an application that uses the bridge sensor is shown below.

In order to draw the best performance of Analog-to-Digital Converter (ADC), the customer is careful about the printed circuit board (PCB) layout pattern and a bypass capacitor placement.

The PCB layout pattern example of NJU9103 is shown below.

GND of decoupling capacitor and GND of NJU9103 make to equipotential as much as possible.

If the noise source and the NJU9103 is mounted on the same PCB, GND of the noise source and GND of NJU9103 separate until just before the GND Pin (connector).

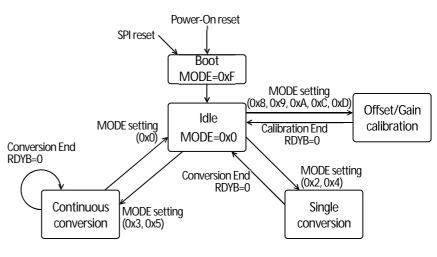

#### **■** Conversion Control

Set the conversion operation by MODE [3: 0] bit of CTRL register.

| MODE[3:0] | OPERATION                    |

|-----------|------------------------------|

| 0x0       | Idle                         |

| 0x1       | Not used                     |

| 0x2       | Single conversion            |

| 0x3       | Continuous conversion        |

| 0x4       | Single conversion + CHOP     |

| 0x5       | Continuous conversion + CHOP |

| 0x6, 0x7  | Not used                     |

| 0x8       | Calibration ADC offset       |

| 0x9       | Calibration ADC gain         |

| 0xA       | Calibration PGA offset       |

| 0xB       | Not used                     |

| 0xC       | Calibration system offset    |

| 0xD       | Calibration system gain      |

| 0xE       | Not used                     |

| 0xF       | Boot                         |

|           |                              |

#### < Definition of time >

(1) ADC conversion time of basic: Tadc

$$T_{adc} = \frac{OSR}{FMOD}$$

OSR : Over Sampling Rate

FMOD : Clock Frequency of ADC

(2) Calculation time for data correction (after ADC conversion): Tcal

$$T_{cal} = \frac{40}{FOSC}$$

FOSC : Clock Frequency of Internal Oscillator

(3) Calculation time for gain coefficient (after gain calibration): T<sub>div</sub>

$$T_{div} = 70/FOSC$$

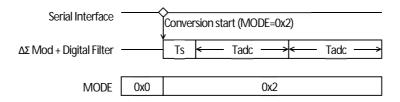

(4) Setup time: Ts

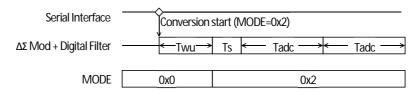

When the analog block is ON (AUTOSLP bit of OPTION 0 register = "0"), setting the MODE [3: 0] bit in CTRL register to operation mode starts operation after Ts (about  $10\mu s$ ). The case where the MODE [3: 0] bit is switched from "sleep (0x0)" to "single conversion (0x2)" is shown below.

(5) Startup wait time: Twu

Waiting time of Twu (about 70µs) is required when changing the analog block from OFF to ON (AUTOSLP bit from "1" to "0"). The figure below shows the case where the MODE [3: 0] bit is switched from "sleep (0x0)" to "single conversion (0x2)".

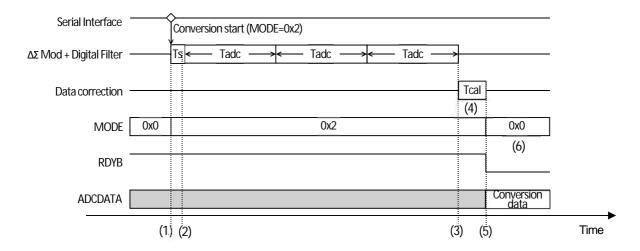

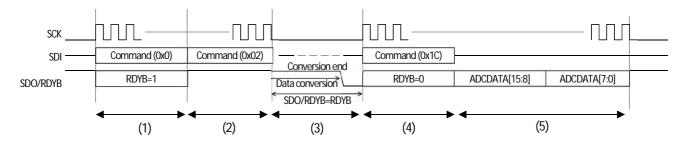

## 1. Single Conversion operation (MODE[3:0] = 0x2)

It is the basic conversion of NJU9103.

Even if the input signal is switched by the multiplexer (external), waiting time for converted data is unnecessary. (1 settling, zero latency)

When the conversion cycle is long, the recommended usage is that converting once and power-down the remaining period. So, the consumption current of NJU9103 can be reduced. It is the optimum conversion method for "switching input signals with multiplexer" and "low power consumption".

| STEP | DETAILS                                                                                                      |

|------|--------------------------------------------------------------------------------------------------------------|

| (1)  | Set to single conversion. (MODE [3: 0] bit in CTRL register = "0x2")                                         |

| (2)  | After the set-up time (Ts), start the conversion.                                                            |

|      | Conversion completed with conversion time (3 x Tadc).                                                        |

| (3)  | The conversion data is the result of the convolution integration of 3 x Tadc. ( $\Delta\Sigma$ Mod + Digital |

|      | Filter)                                                                                                      |

| (4)  | Data is corrected with calculation time (Tcal).                                                              |

| (E)  | Conversion data stored in ADCDATA register.                                                                  |

| (5)  | At that time, RDYB bit changes from "1" to "0".                                                              |

| (6)  | Shift to Idle state. (MODE[3:0] bit= "0x0")                                                                  |

In NJU9103, the data rate is specified by the following formula. (Single conversion)

$$DR = F_{OSC} \times \frac{1}{OSR} \times \frac{1}{2^{(CLKDIV+1)}} \times \frac{1}{3}$$

The conversion data rate (DR) is DR\_all when Ts and Tcal are considered. (In the table below, CLKDIV=0)

| OSR | DR [sps] | 3xTadc(=1/DR) [s] | 3xTadc+Ts+Tcal [s] | DR_all (=1/(3xTadc+Ts+Tcal)) [sps] |  |

|-----|----------|-------------------|--------------------|------------------------------------|--|

| 512 | 0.814k   | 1.23m             | 1.26m              | 0.794k                             |  |

| 256 | 1.63k    | 0.614m            | 0.640m             | 1.56k                              |  |

| 128 | 3.26k    | 0.307m            | 0.333m             | 3.00k                              |  |

| 64  | 6.51k    | 0.154m            | 0.180m             | 5.56k                              |  |

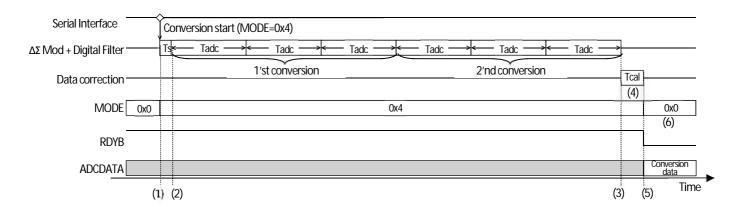

## 2. "Single conversion + CHOP" operation (MODE[3:0] = 0x4)

Single conversion performs single conversion twice. By change VINP and VINN at the second conversion, the NJU9103 offset can be removed in real time. The change of VINP and NINN is done automatically by the internal switch.

With single conversion, it is the optimum conversion method for "when you want to calibrate the offset in real time". Though, the data rate is half of single conversion.

| STEP | DETAILS                                                                                    |  |  |  |

|------|--------------------------------------------------------------------------------------------|--|--|--|

| (1)  | Set to single conversion + CHOP. (MODE [3: 0] bit in CTRL register = "0x4")                |  |  |  |

| (2)  | After the set-up time (Ts), start the conversion.                                          |  |  |  |

|      | Conversion completed in conversion time (6 x Tadc).                                        |  |  |  |

| (3)  | The conversion data is the result of the convolution integration of 6 x Tadc. (1'st & 2'nd |  |  |  |

|      | conversion of "ΔΣ Mod + Digital Filter".)                                                  |  |  |  |

| (4)  | Data is corrected in calculation time (Tcal).                                              |  |  |  |

| (5)  | Conversion data stored in ADCDATA register.                                                |  |  |  |

| (5)  | At that time, RDYB bit changes from "1" to "0".                                            |  |  |  |

| (6)  | Shift to Idle state. (MODE[3:0] bit= "0x0")                                                |  |  |  |

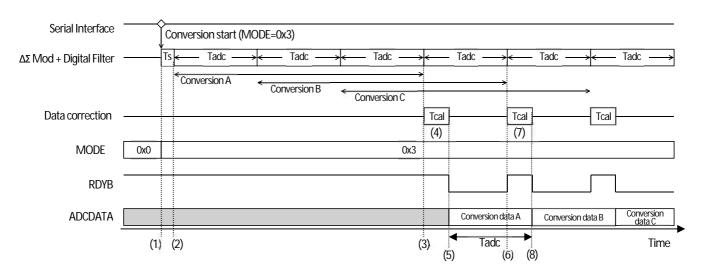

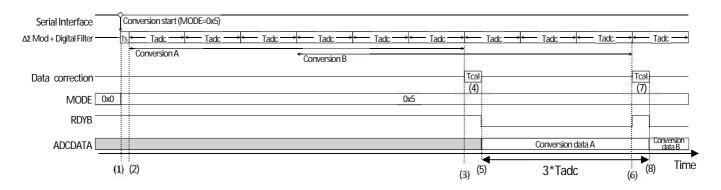

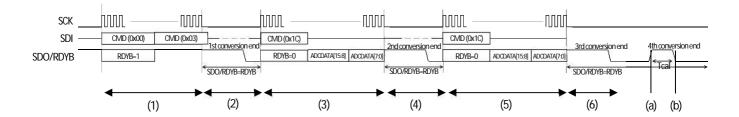

## 3. Continuous conversion operation (MODE[3:0] = 0x3)

When input signals are switched by the multiplexer, the same waiting time as the first conversion (conversion A) is required. When input signal is not switched by multiplexer, wait time after the second conversion (conversion B) is unnecessary.

It is the optimum conversion method for "when input is not switched by multiplexer" and "when you want to maximize data rate". The data rate is three times that of single conversion.

| STEP | DETAILS                                                                                           |  |  |  |  |

|------|---------------------------------------------------------------------------------------------------|--|--|--|--|

| (1)  | Set to continuous conversion. (MODE [3: 0] bit in CTRL register = "0x3")                          |  |  |  |  |

| (2)  | After the set-up time (Ts), start the conversion.                                                 |  |  |  |  |

|      | Conversion A (1'st) completed in conversion time (3 x Tadc).                                      |  |  |  |  |

| (3)  | The conversion data A is the result of the convolution integration of conversion A ("3 x Tadc" of |  |  |  |  |

|      | ΔΣ Mod + Digital Filter")                                                                         |  |  |  |  |

| (4)  | Data is corrected in calculation time (Tcal)                                                      |  |  |  |  |

| (E)  | Conversion data A (1'st) stored in ADCDATA register.                                              |  |  |  |  |

| (5)  | At that time, RDYB bit changes from "1" to "0".                                                   |  |  |  |  |

|      | After completion of conversion B (2'nd), RDYB bit changes from "0" to "1".                        |  |  |  |  |

| (6)  | The conversion data B is the result of the convolution integration of conversion B ("3 x Tadc" of |  |  |  |  |

|      | ΔΣ Mod + Digital Filter)                                                                          |  |  |  |  |

| (7)  | Data is corrected in calculation time (Tcal).                                                     |  |  |  |  |

| (9)  | Conversion data B (2'nd) stored (overwrite) in ADCDATA register.                                  |  |  |  |  |

| (8)  | At that time, RDYB bit changes from "1" to "0".                                                   |  |  |  |  |

Repeat steps (5) to (8) until the operation mode is set to idle (MODE [3: 0] bit is set to "0x0").

## 4. "Continuous conversion + CHOP" operation (MODE[3:0] = 0x5)

By changing VINP and VINN every "3 x Tadc", the NJU9103 offset can be removed in real time. The change of VINP and VINN is done automatically by the internal switch.

When input signals are switched by the multiplexer, the same waiting time as the first conversion (conversion A) is required. When input signal is not switched by multiplexer, wait time after the second conversion (conversion B) is unnecessary.

As with "single conversion + CHOP" operation, offset of whole chip can be calibrated in real time.

It is the optimal conversion method for "when you want to calibrate offsets in real time" with continuous conversion. Though, the data rate is 1/3 of continuous conversion. (Same data rate as single conversion)

| STEP | DETAILS                                                                                           |  |  |  |  |  |

|------|---------------------------------------------------------------------------------------------------|--|--|--|--|--|

| (1)  | Set to continuous conversion + CHOP. (MODE [3: 0] bit in CTRL register = "0x5")                   |  |  |  |  |  |

| (2)  | After the set-up time (Ts), start the conversion.                                                 |  |  |  |  |  |

|      | Conversion A (1'st) completed in conversion time (6 x Tadc).                                      |  |  |  |  |  |

| (3)  | The conversion data A is the result of the convolution integration of conversion A ("6 x Tadc" of |  |  |  |  |  |

|      | ΔΣ Mod + Digital Filter")                                                                         |  |  |  |  |  |

| (4)  | Data is corrected in calculation time (Tcal).                                                     |  |  |  |  |  |

| (5)  | Conversion data A (1'st) stored in ADCDATA register.                                              |  |  |  |  |  |

| (5)  | At that time, RDYB bit changes from "1" to "0".                                                   |  |  |  |  |  |

|      | After completion of conversion B (2'nd), RDYB bit changes from "0" to "1".                        |  |  |  |  |  |

| (6)  | The conversion data B is the result of the convolution integration of conversion B ("6 x Tadc" of |  |  |  |  |  |

|      | ΔΣ Mod + Digital Filter)                                                                          |  |  |  |  |  |

| (7)  | Data is corrected in calculation time (Tcal).                                                     |  |  |  |  |  |

| (0)  | Conversion data B (2'nd) stored (overwrite) in ADCDATA register.                                  |  |  |  |  |  |

| (8)  | At that time, RDYB bit changes from "1" to "0".                                                   |  |  |  |  |  |

Repeat steps (5) to (8) until the operation mode is set to idle (MODE [3: 0] bit is set to "0x0").

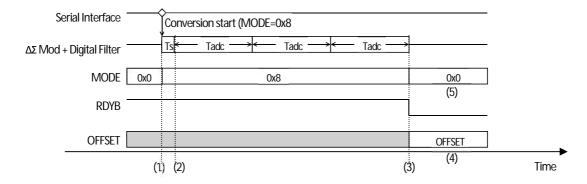

## 5. Offset calibration operation (MODE[3:0] = 0x8, 0xA, 0xC)

Timing is almost the same as single conversion operation.

Calculate the offset amount and save it in the OFFSET register (OFFSET0, OFFSET1, and OFFSET2).

| STEP | DETAILS                                                                           |  |  |  |

|------|-----------------------------------------------------------------------------------|--|--|--|

| (1)  | Set to offset calibration. (MODE [3: 0] bit in CTRL register = 0x8 or 0xA or 0xC) |  |  |  |

| (2)  | After the set-up time (Ts), start the conversion.                                 |  |  |  |

| (3)  | Conversion is complete in conversion time (3 xTadc).                              |  |  |  |

| (4)  | Conversion data stored in OFFSET register (OFFSET0, OFFSET1, OFFSET2).            |  |  |  |

| (4)  | At that time, RDYB bit changes from "1" to "0".                                   |  |  |  |

| (5)  | Shift to Idle state. (MODE[3:0] bit= "0x0")                                       |  |  |  |

The NJU 9103 supports the following three types of offset calibration operation.

#### A. Internal offset calibration (MODE[3:0] = 0x8)

When the internal offset calibration command is executed, the following processing is automatically performed.

- Set PGA1 to OFF and set the PGA2 gain to "x1".

- · Applying GND internally to IN+ and IN- of the ADC to calculate the offset.

- · Store calculated offset in OFFSET registers.

## B. PGA1 offset calibration (MODE[3:0] = 0xA)

Set the gain of PGA1 and PGA2 before executing the PGA1 offset calibration command.

When the PGA1 offset calibration command is executed, the following processing is automatically performed.

- · Connect VINN to the plus and minus inputs of PGA 1 and calculate the offset.

- · Store calculated offset in OFFSET registers.

## C. System offset calibration (MODE[3:0] = 0xC)

CHSEL [2: 0] bit selects the input channel.

When the system offset calibration command is executed, the following processing is automatically performed.

- · Calculate the offset using the input channel selected with the CHSEL [2: 0] bits.

- · Store calculated offset in OFFSET registers.

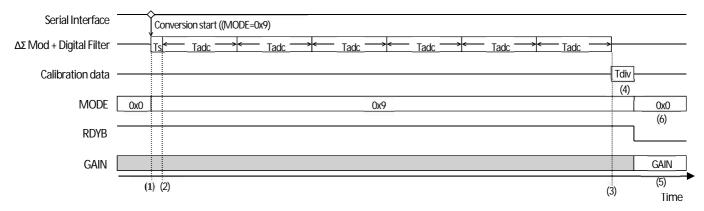

## 6. Gain calibration operation (MODE[3:0] = 0x9, 0xD)

Timing is almost the same as "single conversion + CHOP" operation.

Calculate the gain factor and save it in the GAIN register (GAIN0, GAIN1, and GAIN2).

| STEP | DETAILS                                                                                     |  |  |  |

|------|---------------------------------------------------------------------------------------------|--|--|--|

| (1)  | Set to gain calibration. (MODE [3: 0] bit in CTRL register = 0x9 or 0xD)                    |  |  |  |

| (2)  | After the set-up time (Ts), start the conversion.                                           |  |  |  |

| (3)  | Conversion is complete in conversion time (6 xTadc).                                        |  |  |  |

| (4)  | The slope (gain) coefficient is calculated in the gain coefficient calculation time (Tdiv). |  |  |  |

| (E)  | The GAIN registers (GAIN 0, GAIN 1, GAIN 2) are updated.                                    |  |  |  |

| (5)  | At that time, RDYB bit changes from "1" to "0".                                             |  |  |  |

| (6)  | Shift to Idle state. (MODE[3:0] bit= "0x0")                                                 |  |  |  |

The NJU 9103 supports the following two types of gain calibration operation.

#### A. Internal gain calibration (MODE[3:0] = 0x9)

When the internal gain calibration command is executed, the following processing is automatically performed.

- Set PGA1 to OFF and set the PGA2 gain to "x1".

- · Internally supply VREF and GND to the input of the ADC to calculate the gain coefficient.

- · Store calculated gain coefficient in GAIN registers.

## B. System gain calibration (MODE[3:0] = 0xD)

CHSEL [2: 0] bit selects the input channel.

When the system gain calibration command is executed, the following processing is automatically performed.

- · Calculate the gain coefficient so that the input selected with the CHSEL [2: 0] bits becomes full scale.

- · Store calculated gain coefficient in GAIN registers.

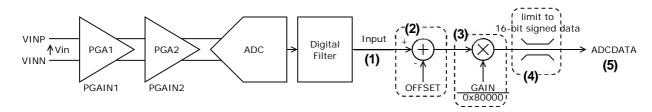

#### ■ Data Calibration Flow / Combination of conversion operation and calibration operation

"Flow of data proofreading" and "Combination of conversion operation and calibration operation" are explained.

## 1. Single conversion or Continuous conversion

The figure below is a calibration flow block diagram of "single conversion" or "continuous conversion".

The offset calibration uses the value of the offset register (OFFSET0, OFFSET1, OFFSET2).

The gain calibration uses the values of the gain register (GAIN0, GAIN1, GAIN2).

| STEP | DETAILS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|      | "Input" is the following value with respect to the input voltage Vin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|      | The full scale of the digital filter is eight times signed 16 bits (262144 = 32768 x 8).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| (1)  | $Input = \frac{V_{in}}{VREF} \times PGAIN1 \times PGAIN2 \times 262144$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| (2)  | Subtract "OFFSET" calculated by offset calibration operation from "Input".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| (2)  | Multiply the result of step (2) by "GAIN" calculated by the gain calibration operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| (3)  | In order to convert to signed 16-bit full scale, $1/(0x 800,000) = 1/(32768 \times 8)$ is also multiplied.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|      | Confirm whether "-32768 ≤ (3) result ≤ +32768" is satisfied.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| (4)  | If it is not satisfied, set the OV bit of the CTRL register to "1".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|      | If it is satisfied, set the OV bit of the CTRL register to "0".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|      | Store the calculation result in the ADCDATA register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| (5)  | If "OV=1" in step (4), the ADCDATA register is the minimum value (-32768) or the maximum value (+32767).                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|      | $ADCDATA = \left(Input - OFFSET\right) \times \frac{GAIN}{0x80000} = \left(\frac{V_{in}}{VREF} \times PGAIN1 \times PGAIN2 \times 262144 - OFFSET\right) \times \frac{GAIN}{0x800000} = \left(\frac{V_{in}}{VREF} \times PGAIN1 \times PGAIN2 \times 262144 - OFFSET\right) \times \frac{GAIN}{0x800000} = \left(\frac{V_{in}}{VREF} \times PGAIN1 \times PGAIN2 \times 262144 - OFFSET\right) \times \frac{GAIN}{0x8000000} = \left(\frac{V_{in}}{VREF} \times PGAIN1 \times PGAIN2 \times 262144 - OFFSET\right) \times \frac{GAIN}{0x800000000000000000000000000000000000$ |  |  |  |  |  |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |